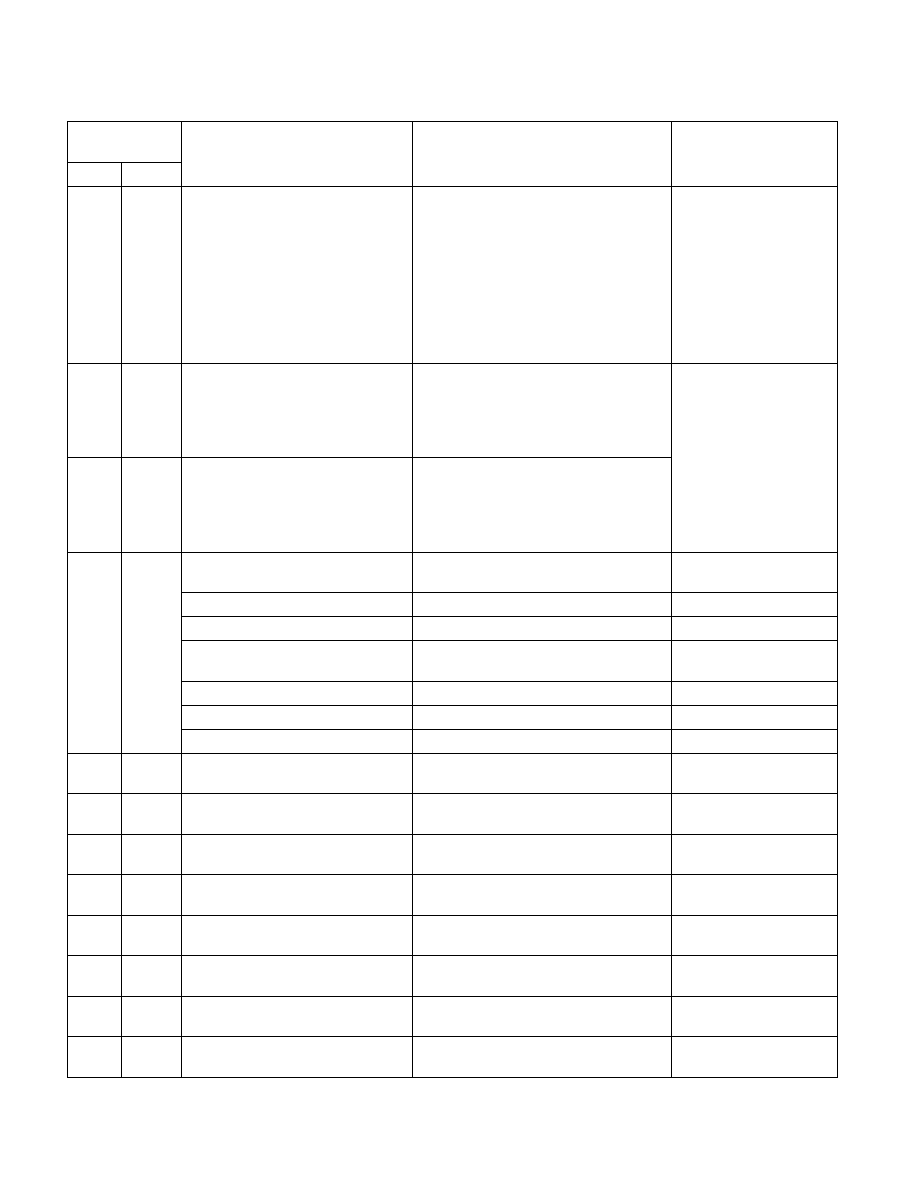

35-6 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

8DH

141

IA32_SGXLEPUBKEYHASH1

IA32_SGXLEPUBKEYHASH[127:64] (R/W)

Bits 127:64 of the SHA256 digest of the

SIGSTRUCT.MODULUS for SGX Launch

Enclave. On reset, the default value is the

digest of Intel’s signing key.

Read permitted If

CPUID.(EAX=12H,ECX=0H):

EAX[0]=1,

Write permitted if

CPUID.(EAX=12H,ECX=0H):

EAX[0]=1 &&

IA32_FEATURE_CONTROL[

17] = 1 &&

IA32_FEATURE_CONTROL[

0] = 1

8EH

142

IA32_SGXLEPUBKEYHASH2

IA32_SGXLEPUBKEYHASH[191:128] (R/W)

Bits 191:128 of the SHA256 digest of the

SIGSTRUCT.MODULUS for SGX Launch

Enclave. On reset, the default value is the

digest of Intel’s signing key.

Read permitted If

CPUID.(EAX=12H,ECX=0H):

EAX[0]=1,

Write permitted if

CPUID.(EAX=12H,ECX=0H):

EAX[0]=1 &&

IA32_FEATURE_CONTROL[

17] = 1 &&

IA32_FEATURE_CONTROL[

0] = 1

8FH

143

IA32_SGXLEPUBKEYHASH3

IA32_SGXLEPUBKEYHASH[255:192] (R/W)

Bits 255:192 of the SHA256 digest of the

SIGSTRUCT.MODULUS for SGX Launch

Enclave. On reset, the default value is the

digest of Intel’s signing key.

9BH

155

IA32_SMM_MONITOR_CTL

SMM Monitor Configuration (R/W)

If CPUID.01H: ECX[5]=1 ||

CPUID.01H: ECX[6] = 1

0

Valid (R/W)

1

Reserved

2

Controls SMI unblocking by VMXOFF (see

If IA32_VMX_MISC[28]

11:3

Reserved

31:12

MSEG Base (R/W)

63:32

Reserved

9EH

158

IA32_SMBASE

Base address of the logical processor’s

SMRAM image (RO, SMM only)

If IA32_VMX_MISC[15]

C1H

193

IA32_PMC0 (PERFCTR0)

General Performance Counter 0 (R/W)

If CPUID.0AH: EAX[15:8] >

0

C2H

194

IA32_PMC1 (PERFCTR1)

General Performance Counter 1 (R/W)

If CPUID.0AH: EAX[15:8] >

1

C3H

195

IA32_PMC2

General Performance Counter 2 (R/W)

If CPUID.0AH: EAX[15:8] >

2

C4H

196

IA32_PMC3

General Performance Counter 3 (R/W)

If CPUID.0AH: EAX[15:8] >

3

C5H

197

IA32_PMC4

General Performance Counter 4 (R/W)

If CPUID.0AH: EAX[15:8] >

4

C6H

198

IA32_PMC5

General Performance Counter 5 (R/W)

If CPUID.0AH: EAX[15:8] >

5

C7H

199

IA32_PMC6

General Performance Counter 6 (R/W)

If CPUID.0AH: EAX[15:8] >

6

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal