Vol. 3C 35-5

MODEL-SPECIFIC REGISTERS (MSRS)

20

LMCE On (R/WL): When set, system

software can program the MSRs associated

with LMCE to configure delivery of some

machine check exceptions to a single logical

processor.

If IA32_MCG_CAP[27] = 1

63:21

Reserved

3BH

59

IA32_TSC_ADJUST

Per Logical Processor TSC Adjust (R/Write

to clear)

If CPUID.(EAX=07H,

ECX=0H): EBX[1] = 1

63:0

THREAD_ADJUST:

Local offset value of the IA32_TSC for a

logical processor. Reset value is Zero. A

write to IA32_TSC will modify the local

offset in IA32_TSC_ADJUST and the

content of IA32_TSC, but does not affect

the internal invariant TSC hardware.

79H

121

IA32_BIOS_UPDT_TRIG

(BIOS_UPDT_TRIG)

BIOS Update Trigger (W)

Executing a WRMSR instruction to this MSR

causes a microcode update to be loaded

into the processor. See Section 9.11.6,

“Microcode Update Loader.”

A processor may prevent writing to this

MSR when loading guest states on VM

entries or saving guest states on VM exits.

06_01H

8BH

139

IA32_BIOS_SIGN_ID

(BIOS_SIGN/BBL_CR_D3)

BIOS Update Signature (RO)

Returns the microcode update signature

following the execution of CPUID.01H.

A processor may prevent writing to this

MSR when loading guest states on VM

entries or saving guest states on VM exits.

06_01H

31:0

Reserved

63:32

It is recommended that this field be pre-

loaded with 0 prior to executing CPUID.

If the field remains 0 following the

execution of CPUID; this indicates that no

microcode update is loaded. Any non-zero

value is the microcode update signature.

8CH

140

IA32_SGXLEPUBKEYHASH0

IA32_SGXLEPUBKEYHASH[63:0] (R/W)

Bits 63:0 of the SHA256 digest of the

SIGSTRUCT.MODULUS for SGX Launch

Enclave. On reset, the default value is the

digest of Intel’s signing key.

Read permitted If

CPUID.(EAX=12H,ECX=0H):

EAX[0]=1,

Write permitted if

CPUID.(EAX=12H,ECX=0H):

EAX[0]=1 &&

IA32_FEATURE_CONTROL[

17] = 1 &&

IA32_FEATURE_CONTROL[

0] = 1

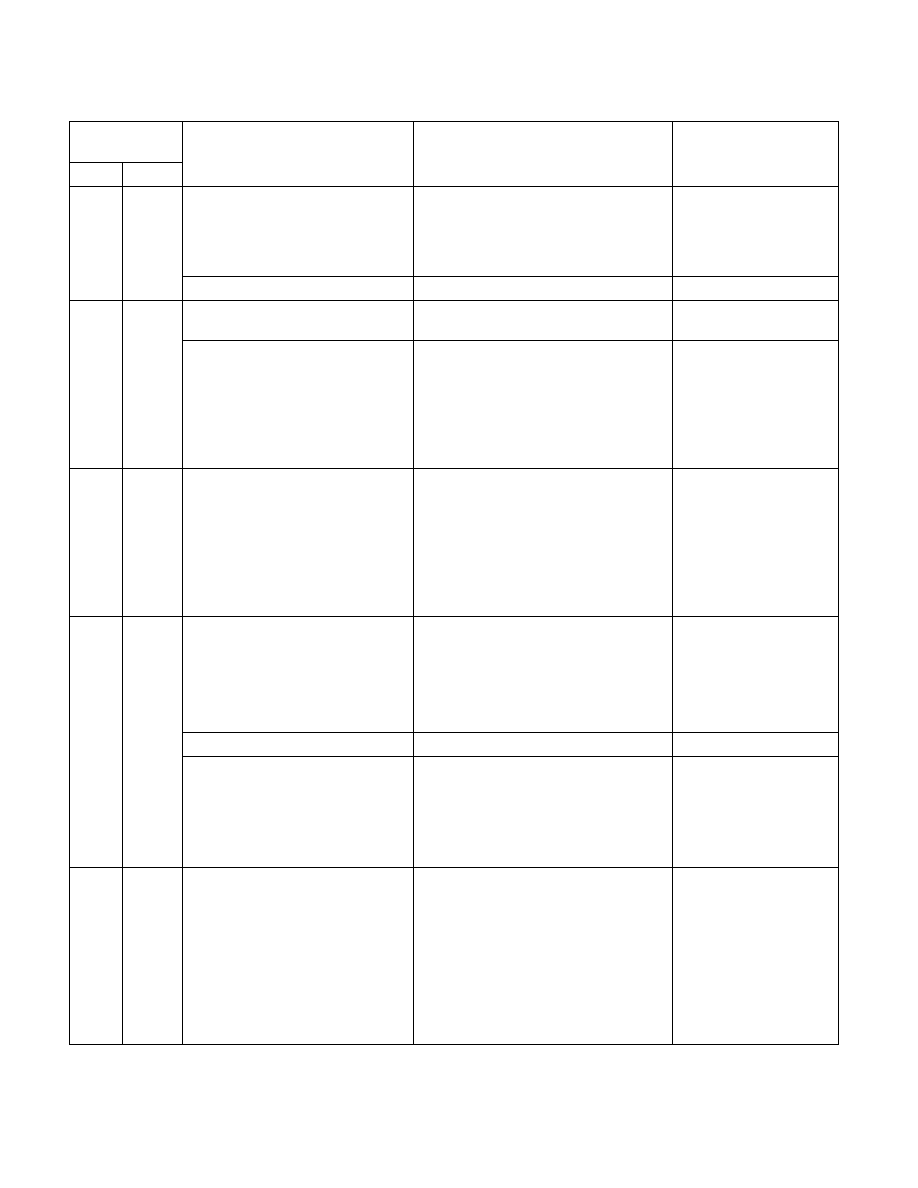

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal