Vol. 3C 34-21

SYSTEM MANAGEMENT MODE

•

Guest linear address. This field is used for VM exits due to SMIs that arrive immediately after the retirement

of an INS or OUTS instruction for which the relevant segment (ES for INS; DS for OUTS unless overridden by

an instruction prefix) is usable. The field receives the value of the linear address generated by ES:(E)DI (for

INS) or segment:(E)SI (for OUTS; the default segment is DS but can be overridden by a segment override

prefix) at the time the instruction started. If the relevant segment is not usable, the value is undefined. On

processors that support Intel 64 architecture, bits 63:32 are clear if the logical processor was not in 64-bit

mode before the VM exit.

•

I/O RCX, I/O RSI, I/O RDI, and I/O RIP. For an SMM VM exit due an SMI that arrives immediately after

the retirement of an I/O instruction, these fields receive the values that were in RCX, RSI, RDI, and RIP, respec-

tively, before the I/O instruction executed. Thus, the value saved for I/O RIP addresses the I/O instruction.

34.15.2.4 Saving Guest State

SMM VM exits save the contents of the SMBASE register into the corresponding field in the guest-state area.

The value of the VMX-preemption timer is saved into the corresponding field in the guest-state area if the “save

VMX-preemption timer value” VM-exit control is 1. That field becomes undefined if, in addition, either the SMM

VM exit is from VMX root operation or the SMM VM exit is from VMX non-root operation and the “activate VMX-

preemption timer” VM-execution control is 0.

34.15.2.5 Updating Non-Register State

SMM VM exits affect the non-register state of a logical processor as follows:

•

SMM VM exits cause non-maskable interrupts (NMIs) to be blocked; they may be unblocked through execution

of IRET or through a VM entry (depending on the value loaded for the interruptibility state and the setting of

the “virtual NMIs” VM-execution control).

•

SMM VM exits cause SMIs to be blocked; they may be unblocked by a VM entry that returns from SMM (see

Section 34.15.4).

SMM VM exits invalidate linear mappings and combined mappings associated with VPID 0000H for all PCIDs.

Combined mappings for VPID 0000H are invalidated for all EP4TA values (EP4TA is the value of bits 51:12 of EPTP;

see Section 28.3). (Ordinary VM exits are not required to perform such invalidation if the “enable VPID” VM-execu-

tion control is 1; see Section 27.5.5.)

34.15.3 Operation of the SMM-Transfer Monitor

Once invoked, the SMM-transfer monitor (STM) is in VMX root operation and can use VMX instructions to configure

VMCSs and to cause VM entries to virtual machines supported by those structures. As noted in Section 34.15.1, the

VMXOFF instruction cannot be used under the dual-monitor treatment and thus cannot be used by the STM.

The RSM instruction also cannot be used under the dual-monitor treatment. As noted in Section 25.1.3, it causes

a VM exit if executed in SMM in VMX non-root operation. If executed in VMX root operation, it causes an invalid-

opcode exception. The STM uses VM entries to return from SMM (see Section 34.15.4).

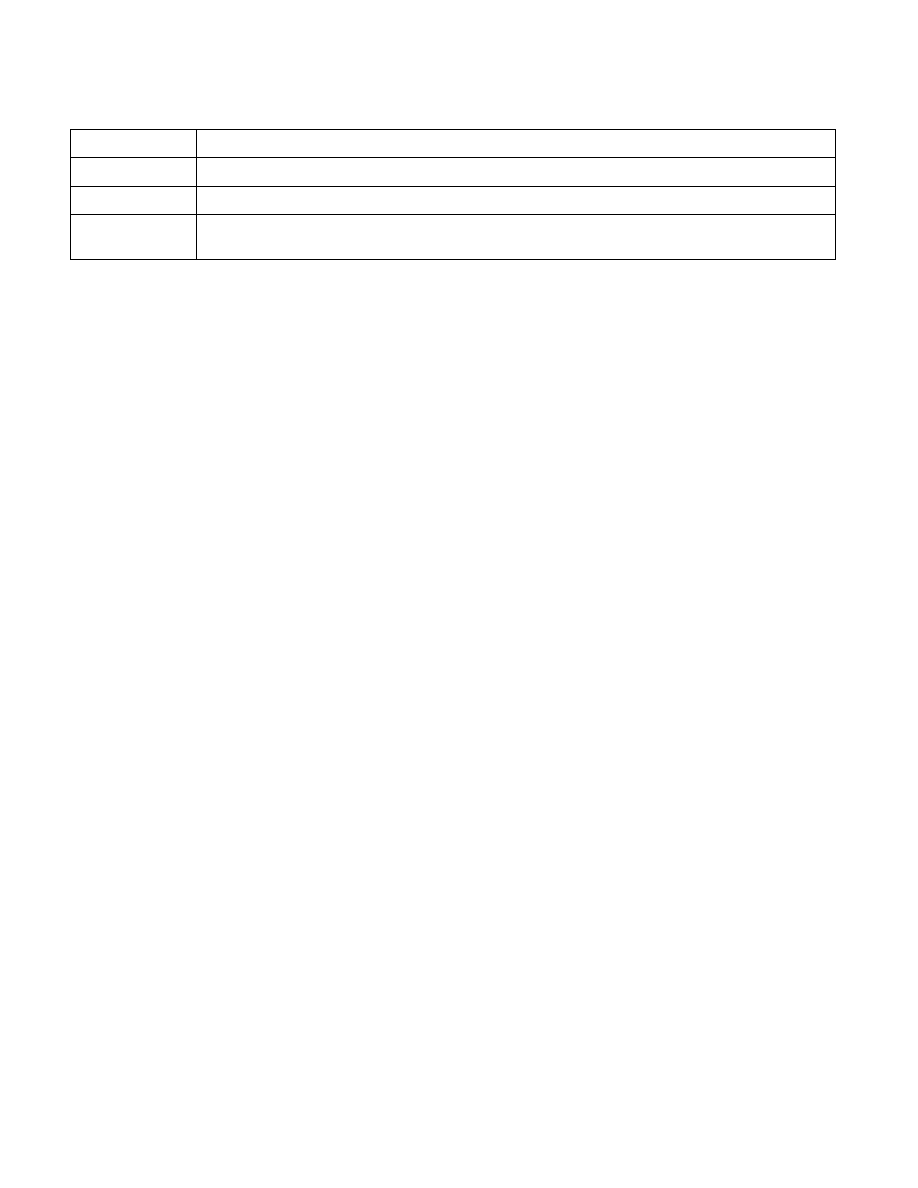

15:7

Reserved (cleared to 0)

31:16

Port number (as specified in the I/O instruction)

63:32

Reserved (cleared to 0). These bits exist only on processors

that support Intel 64 architecture.

Table 34-9. Exit Qualification for SMIs That Arrive Immediately After the Retirement of an I/O Instruction (Contd.)

Bit Position(s)

Contents