Vol. 3C 28-5

VMX SUPPORT FOR ADDRESS TRANSLATION

An EPT page-directory comprises 512 64-bit entries (PDEs). An EPT PDE is selected using the physical address

defined as follows:

— Bits 63:52 are all 0.

— Bits 51:12 are from the EPT PDPTE.

— Bits 11:3 are bits 29:21 of the guest-physical address.

— Bits 2:0 are all 0.

Because an EPT PDE is identified using bits 47:21 of the guest-physical address, it controls access to a 2-MByte

region of the guest-physical-address space. Use of the EPT PDE depends on the value of bit 7 in that entry:

•

If bit 7 of the EPT PDE is 1, the EPT PDE maps a 2-MByte page. The final physical address is computed as

follows:

— Bits 63:52 are all 0.

— Bits 51:21 are from the EPT PDE.

— Bits 20:0 are from the original guest-physical address.

The format of an EPT PDE that maps a 2-MByte page is given in Table 28-4.

•

If bit 7 of the EPT PDE is 0, a 4-KByte naturally aligned EPT page table is located at the physical address

specified in bits 51:12 of the EPT PDE. The format of an EPT PDE that references an EPT page table is given in

Table 28-5.

An EPT page table comprises 512 64-bit entries (PTEs). An EPT PTE is selected using a physical address defined

as follows:

— Bits 63:52 are all 0.

— Bits 51:12 are from the EPT PDE.

— Bits 11:3 are bits 20:12 of the guest-physical address.

— Bits 2:0 are all 0.

•

Because an EPT PTE is identified using bits 47:12 of the guest-physical address, every EPT PTE maps a 4-KByte

page. The final physical address is computed as follows:

— Bits 63:52 are all 0.

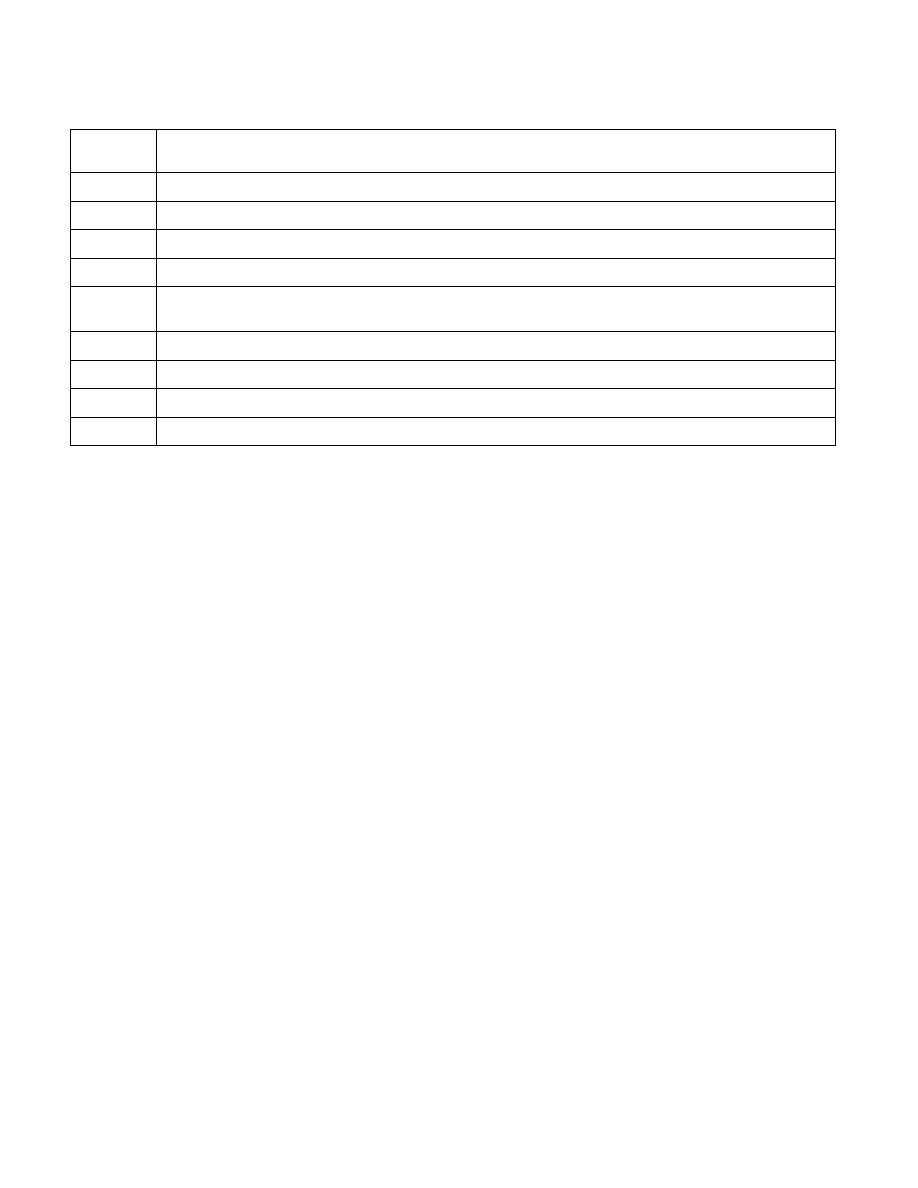

Table 28-3. Format of an EPT Page-Directory-Pointer-Table Entry (PDPTE) that References an EPT Page Directory

Bit

Position(s)

Contents

0

Read access; indicates whether reads are allowed from the 1-GByte region controlled by this entry

1

Write access; indicates whether writes are allowed to the 1-GByte region controlled by this entry

2

Execute access; indicates whether instruction fetches are allowed from the 1-GByte region controlled by this entry

7:3

Reserved (must be 0)

8

If bit 6 of EPTP is 1, accessed flag for EPT; indicates whether software has accessed the 1-GByte region controlled

by this entry (see Section 28.2.4). Ignored if bit 6 of EPTP is 0

11:9

Ignored

(N–1):12

Physical address of 4-KByte aligned EPT page directory referenced by this entry

1

51:N

Reserved (must be 0)

63:52

Ignored

NOTES:

1. N is the physical-address width supported by the logical processor.