Vol. 3A 3-15

PROTECTED-MODE MEMORY MANAGEMENT

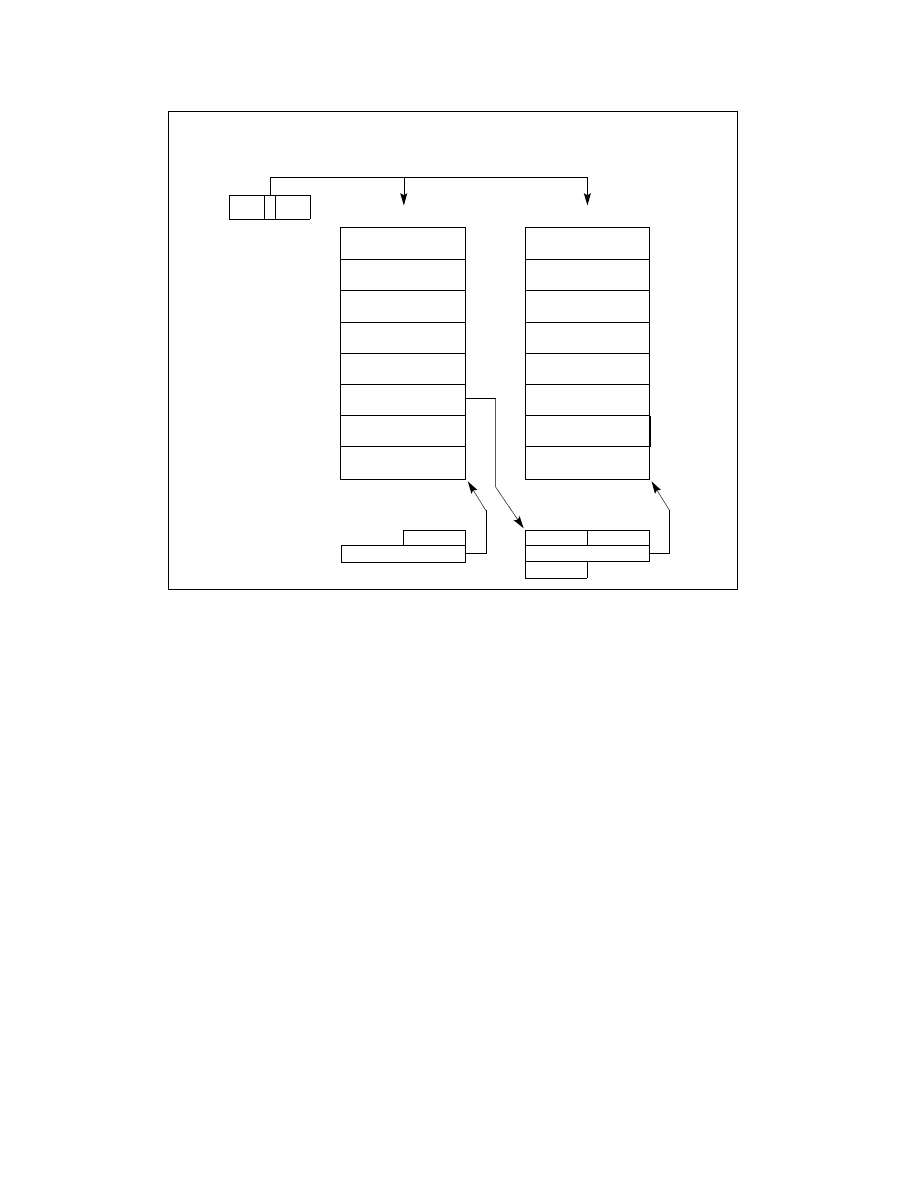

Each system must have one GDT defined, which may be used for all programs and tasks in the system. Optionally,

one or more LDTs can be defined. For example, an LDT can be defined for each separate task being run, or some or

all tasks can share the same LDT.

The GDT is not a segment itself; instead, it is a data structure in linear address space. The base linear address and

limit of the GDT must be loaded into the GDTR register (see Section 2.4, “Memory-Management Registers”). The

base address of the GDT should be aligned on an eight-byte boundary to yield the best processor performance. The

limit value for the GDT is expressed in bytes. As with segments, the limit value is added to the base address to get

the address of the last valid byte. A limit value of 0 results in exactly one valid byte. Because segment descriptors

are always 8 bytes long, the GDT limit should always be one less than an integral multiple of eight (that is, 8N – 1).

The first descriptor in the GDT is not used by the processor. A segment selector to this “null descriptor” does not

generate an exception when loaded into a data-segment register (DS, ES, FS, or GS), but it always generates a

general-protection exception (#GP) when an attempt is made to access memory using the descriptor. By initializing

the segment registers with this segment selector, accidental reference to unused segment registers can be guar-

anteed to generate an exception.

The LDT is located in a system segment of the LDT type. The GDT must contain a segment descriptor for the LDT

segment. If the system supports multiple LDTs, each must have a separate segment selector and segment

descriptor in the GDT. The segment descriptor for an LDT can be located anywhere in the GDT. See Section 3.5,

“System Descriptor Types”, for information on the LDT segment-descriptor type.

An LDT is accessed with its segment selector. To eliminate address translations when accessing the LDT, the

segment selector, base linear address, limit, and access rights of the LDT are stored in the LDTR register (see

Section 2.4, “Memory-Management Registers”).

When the GDTR register is stored (using the SGDT instruction), a 48-bit “pseudo-descriptor” is stored in memory

(see top diagram in Figure 3-11). To avoid alignment check faults in user mode (privilege level 3), the pseudo-

descriptor should be located at an odd word address (that is, address MOD 4 is equal to 2). This causes the

Figure 3-10. Global and Local Descriptor Tables

Segment

Selector

Global

Descriptor

T

First Descriptor in

GDT is Not Used

TI = 0

I

56

40

48

32

24

16

8

0

TI = 1

56

40

48

32

24

16

8

0

Table (GDT)

Local

Descriptor

Table (LDT)

Base Address

Limit

GDTR Register

LDTR Register

Base Address

Seg. Sel.

Limit