Vol. 2A 2-11

INSTRUCTION FORMAT

2.2.1.3

Displacement

Addressing in 64-bit mode uses existing 32-bit ModR/M and SIB encodings. The ModR/M and SIB displacement

sizes do not change. They remain 8 bits or 32 bits and are sign-extended to 64 bits.

2.2.1.4

Direct Memory-Offset MOVs

In 64-bit mode, direct memory-offset forms of the MOV instruction are extended to specify a 64-bit immediate

absolute address. This address is called a moffset. No prefix is needed to specify this 64-bit memory offset. For

these MOV instructions, the size of the memory offset follows the address-size default (64 bits in 64-bit mode). See

Table 2-6.

2.2.1.5

Immediates

In 64-bit mode, the typical size of immediate operands remains 32 bits. When the operand size is 64 bits, the

processor sign-extends all immediates to 64 bits prior to their use.

Support for 64-bit immediate operands is accomplished by expanding the semantics of the existing move (MOV

reg, imm16/32) instructions. These instructions (opcodes B8H – BFH) move 16-bits or 32-bits of immediate data

(depending on the effective operand size) into a GPR. When the effective operand size is 64 bits, these instructions

can be used to load an immediate into a GPR. A REX prefix is needed to override the 32-bit default operand size to

a 64-bit operand size.

For example:

48 B8 8877665544332211 MOV RAX,1122334455667788H

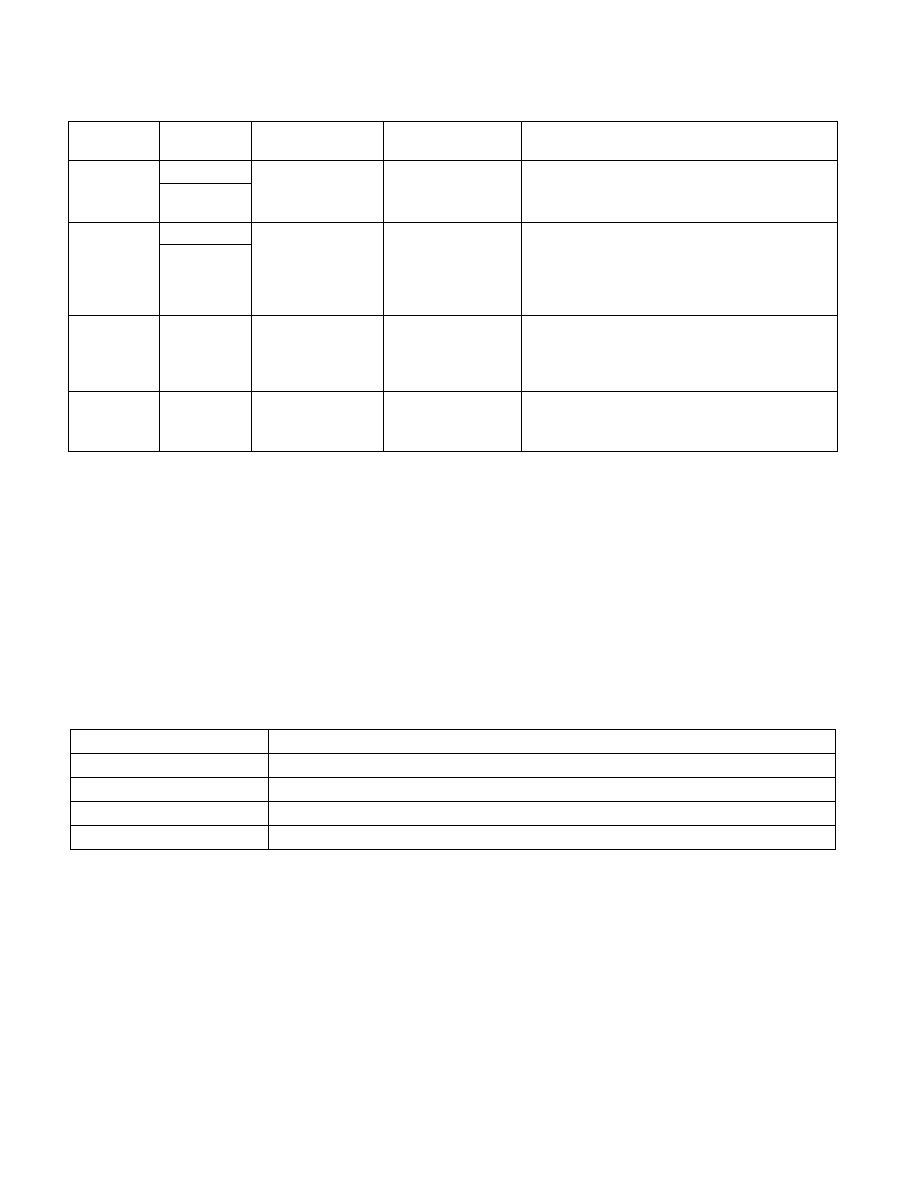

Table 2-5. Special Cases of REX Encodings

ModR/M or

SIB

Sub-field

Encodings

Compatibility Mode

Operation

Compatibility Mode

Implications

Additional Implications

ModR/M Byte mod

≠

11

SIB byte present.

SIB byte required for

ESP-based addressing.

REX prefix adds a fourth bit (b) which is not decoded

(don't care).

SIB byte also required for R12-based addressing.

r/m =

b*100(ESP)

ModR/M Byte mod = 0

Base register not

used.

EBP without a

displacement must be

done using

mod = 01 with

displacement of 0.

REX prefix adds a fourth bit (b) which is not decoded

(don't care).

Using RBP or R13 without displacement must be done

using mod = 01 with a displacement of 0.

r/m =

b*101(EBP)

SIB Byte

index =

0100(ESP)

Index register not

used.

ESP cannot be used as

an index register.

REX prefix adds a fourth bit (b) which is decoded.

There are no additional implications. The expanded

index field allows distinguishing RSP from R12,

therefore R12 can be used as an index.

SIB Byte

base =

0101(EBP)

Base register is

unused if mod = 0.

Base register depends

on mod encoding.

REX prefix adds a fourth bit (b) which is not decoded.

This requires explicit displacement to be used with

EBP/RBP or R13.

NOTES:

* Don’t care about value of REX.B

Table 2-6. Direct Memory Offset Form of MOV

Opcode

Instruction

A0

MOV AL, moffset

A1

MOV EAX, moffset

A2

MOV moffset, AL

A3

MOV moffset, EAX