CPUIDâCPU Identification

INSTRUCTION SET REFERENCE, A-L

Vol. 2A 3-209

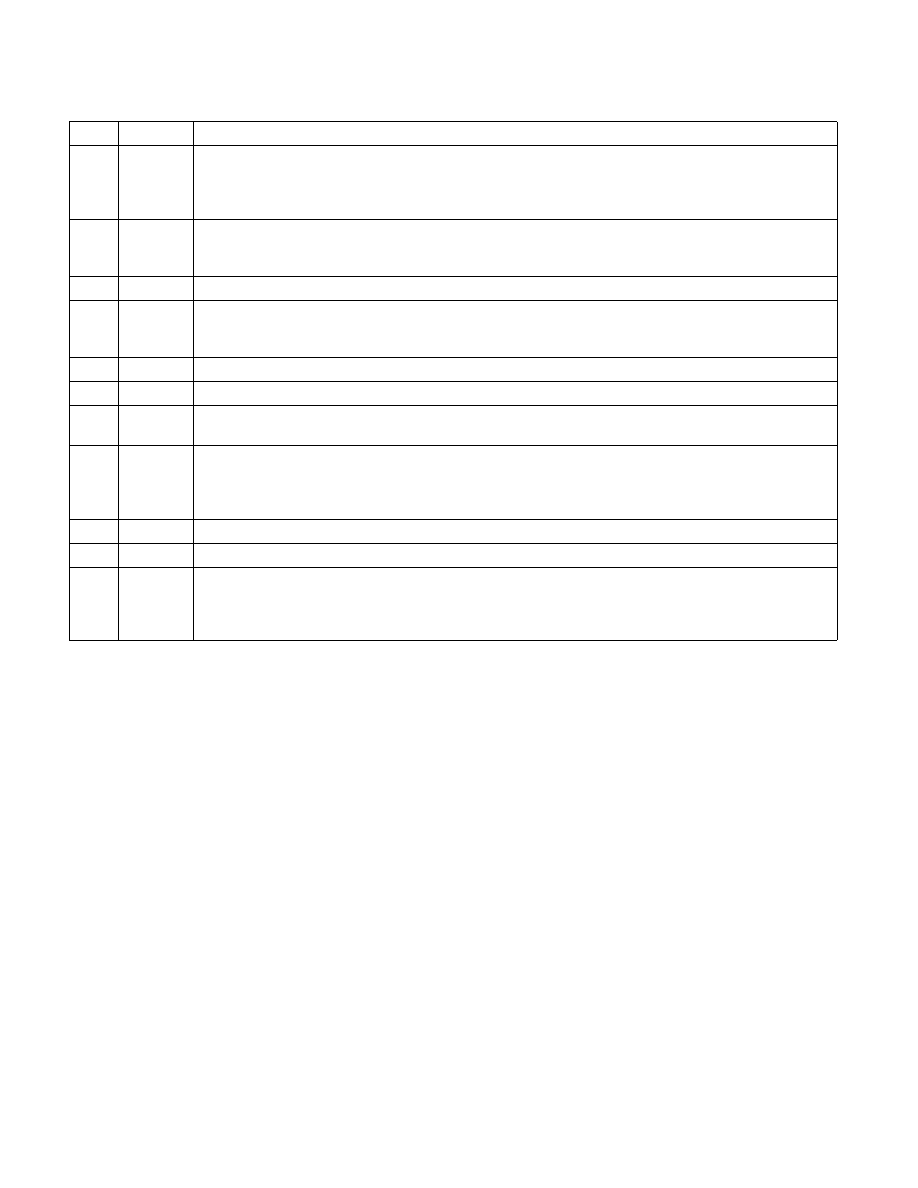

INPUT EAX = 02H: TLB/Cache/Prefetch Information Returned in EAX, EBX, ECX, EDX

When CPUID executes with EAX set to 02H, the processor returns information about the processorâs internal TLBs,

cache and prefetch hardware in the EAX, EBX, ECX, and EDX registers. The information is reported in encoded form

and fall into the following categories:

âĒ

The least-significant byte in register EAX (register AL) will always return 01H. Software should ignore this value

and not interpret it as an informational descriptor.

âĒ

The most significant bit (bit 31) of each register indicates whether the register contains valid information (set

to 0) or is reserved (set to 1).

âĒ

If a register contains valid information, the information is contained in 1 byte descriptors. There are four types

of encoding values for the byte descriptor, the encoding type is noted in the second column of Table 3-12. Table

3-12 lists the encoding of these descriptors. Note that the order of descriptors in the EAX, EBX, ECX, and EDX

registers is not defined; that is, specific bytes are not designated to contain descriptors for specific cache,

prefetch, or TLB types. The descriptors may appear in any order. Note also a processor may report a general

descriptor type (FFH) and not report any byte descriptor of âcache typeâ via CPUID leaf 2.

21 DS

Debug Store. The processor supports the ability to write debug information into a memory resident buffer.

This feature is used by the branch trace store (BTS) and precise event-based sampling (PEBS) facilities (see

Chapter 23, âIntroduction to Virtual-Machine Extensions,â in the IntelÂŪ 64 and IA-32 Architectures Software

Developerâs Manual, Volume 3C).

22 ACPI

Thermal Monitor and Software Controlled Clock Facilities. The processor implements internal MSRs that

allow processor temperature to be monitored and processor performance to be modulated in predefined duty

cycles under software control.

23 MMX

Intel MMX Technology. The processor supports the Intel MMX technology.

24 FXSR

FXSAVE and FXRSTOR Instructions. The FXSAVE and FXRSTOR instructions are supported for fast save and

restore of the floating point context. Presence of this bit also indicates that CR4.OSFXSR is available for an

operating system to indicate that it supports the FXSAVE and FXRSTOR instructions.

25 SSE

SSE. The processor supports the SSE extensions.

26 SSE2

SSE2. The processor supports the SSE2 extensions.

27

SS

Self Snoop. The processor supports the management of conflicting memory types by performing a snoop of its

own cache structure for transactions issued to the bus.

28

HTT

Max APIC IDs reserved field is Valid. A value of 0 for HTT indicates there is only a single logical processor in

the package and software should assume only a single APIC ID is reserved. A value of 1 for HTT indicates the

value in CPUID.1.EBX[23:16] (the Maximum number of addressable IDs for logical processors in this package) is

valid for the package.

29

TM

Thermal Monitor. The processor implements the thermal monitor automatic thermal control circuitry (TCC).

30

Reserved

Reserved

31

PBE

Pending Break Enable. The processor supports the use of the FERR#/PBE# pin when the processor is in the

stop-clock state (STPCLK# is asserted) to signal the processor that an interrupt is pending and that the

processor should return to normal operation to handle the interrupt. Bit 10 (PBE enable) in the

IA32_MISC_ENABLE MSR enables this capability.

Table 3-11. More on Feature Information Returned in the EDX Register (Contd.)

Bit # Mnemonic Description