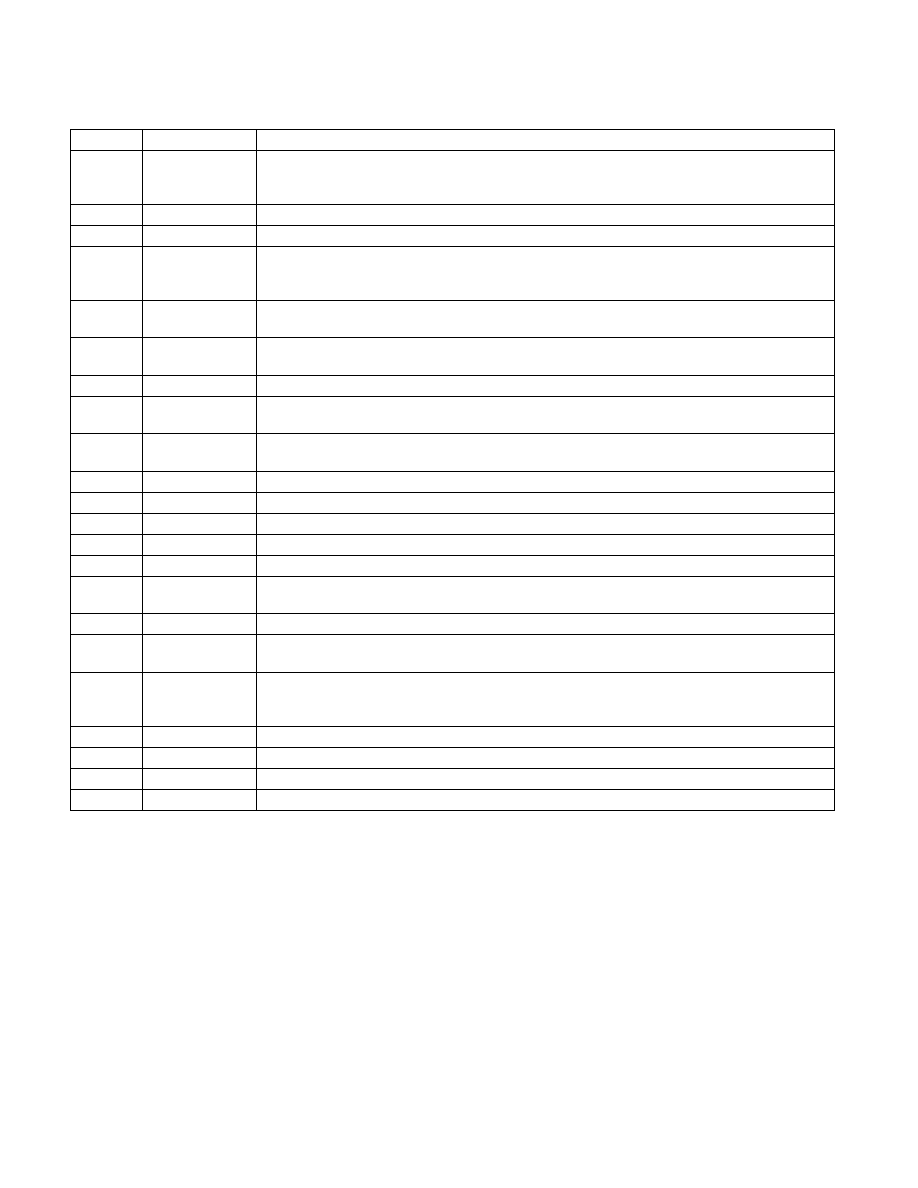

CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

3-206 Vol. 2A

10

CNXT-ID

L1 Context ID. A value of 1 indicates the L1 data cache mode can be set to either adaptive mode

or shared mode. A value of 0 indicates this feature is not supported. See definition of the

IA32_MISC_ENABLE MSR Bit 24 (L1 Data Cache Context Mode) for details.

11

SDBG

A value of 1 indicates the processor supports IA32_DEBUG_INTERFACE MSR for silicon debug.

12

FMA

A value of 1 indicates the processor supports FMA extensions using YMM state.

13

CMPXCHG16B

CMPXCHG16B Available. A value of 1 indicates that the feature is available. See the

“CMPXCHG8B/CMPXCHG16B—Compare and Exchange Bytes” section in this chapter for a

description.

14

xTPR Update

Control

xTPR Update Control. A value of 1 indicates that the processor supports changing

IA32_MISC_ENABLE[bit 23].

15

PDCM

Perfmon and Debug Capability: A value of 1 indicates the processor supports the performance

and debug feature indication MSR IA32_PERF_CAPABILITIES.

16

Reserved

Reserved

17

PCID

Process-context identifiers. A value of 1 indicates that the processor supports PCIDs and that

software may set CR4.PCIDE to 1.

18

DCA

A value of 1 indicates the processor supports the ability to prefetch data from a memory mapped

device.

19

SSE4.1

A value of 1 indicates that the processor supports SSE4.1.

20

SSE4.2

A value of 1 indicates that the processor supports SSE4.2.

21

x2APIC

A value of 1 indicates that the processor supports x2APIC feature.

22

MOVBE

A value of 1 indicates that the processor supports MOVBE instruction.

23

POPCNT

A value of 1 indicates that the processor supports the POPCNT instruction.

24

TSC-Deadline

A value of 1 indicates that the processor’s local APIC timer supports one-shot operation using a

TSC deadline value.

25

AESNI

A value of 1 indicates that the processor supports the AESNI instruction extensions.

26

XSAVE

A value of 1 indicates that the processor supports the XSAVE/XRSTOR processor extended states

feature, the XSETBV/XGETBV instructions, and XCR0.

27

OSXSAVE

A value of 1 indicates that the OS has set CR4.OSXSAVE[bit 18] to enable XSETBV/XGETBV

instructions to access XCR0 and to support processor extended state management using

XSAVE/XRSTOR.

28

AVX

A value of 1 indicates the processor supports the AVX instruction extensions.

29

F16C

A value of 1 indicates that processor supports 16-bit floating-point conversion instructions.

30

RDRAND

A value of 1 indicates that processor supports RDRAND instruction.

31

Not Used

Always returns 0.

Table 3-10. Feature Information Returned in the ECX Register (Contd.)

Bit #

Mnemonic

Description