2-64 Vol. 2A

INSTRUCTION FORMAT

2.7.10

Exception Type E11 (EVEX-only, mem arg no AC, floating-point exceptions)

EVEX-encoded instructions that can cause SIMD FP exception, memory operand support fault suppression but do

not cause #AC follow exception class E11.

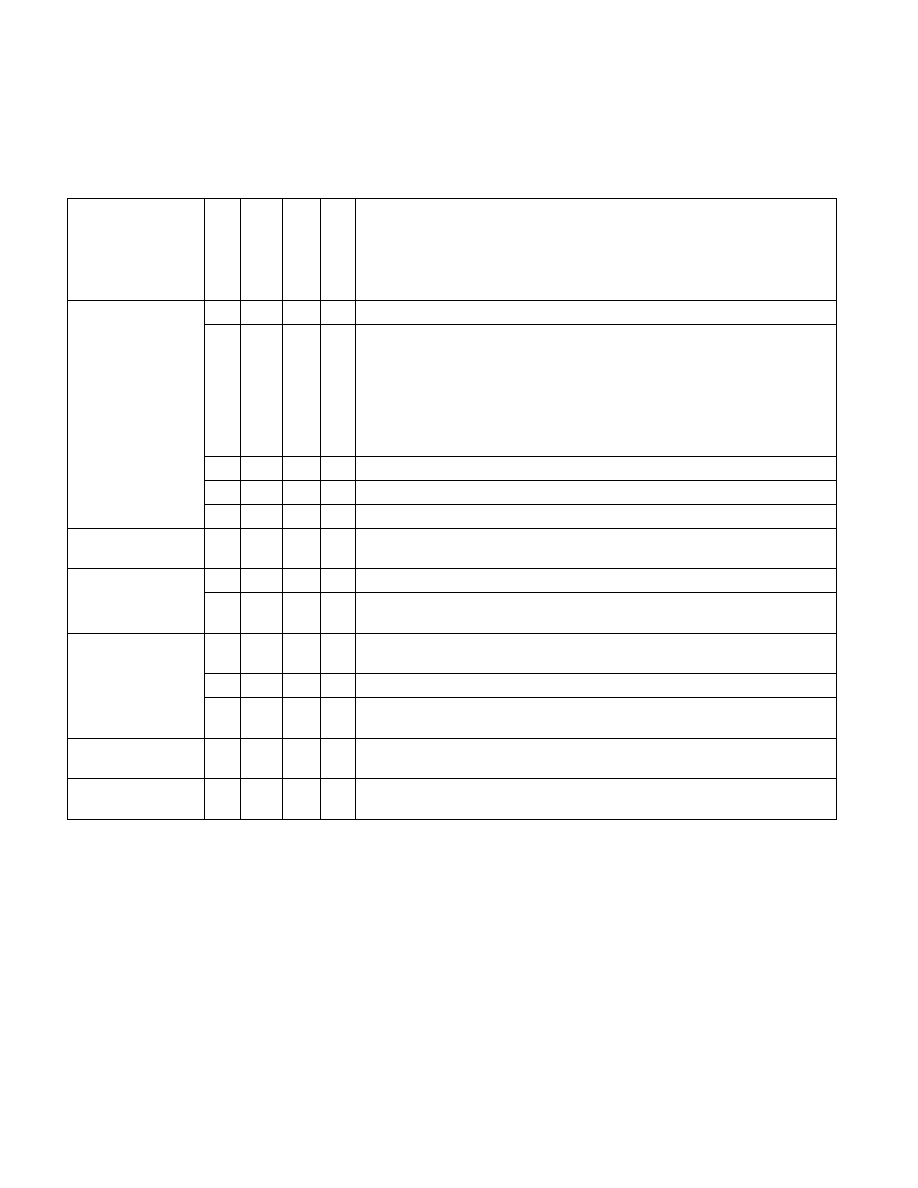

Table 2-60. Type E11 Class Exception Conditions

Exception

Re

al

Virtual 80x86

Pr

ot

ected and

Compatibi

lity

64

-bit

Cause of Exception

Invalid Opcode, #UD

X

X

If EVEX prefix present.

X

X

If CR4.OSXSAVE[bit 18]=0.

If any one of following conditions applies:

• State requirement, Table 2-37 not met.

• Opcode independent #UD condition in Table 2-38.

• Operand encoding #UD conditions in Table 2-39.

• Opmask encoding #UD condition of Table 2-40.

• If EVEX.b != 0.

• If EVEX.L’L != 10b (VL=512).

X

X

X

X

If preceded by a LOCK prefix (F0H).

X

X

If any REX, F2, F3, or 66 prefixes precede a EVEX prefix.

X

X

X

X

If any corresponding CPUID feature flag is ‘0’.

Device Not Available,

#NM

X

X

X

X

If CR0.TS[bit 3]=1.

Stack, SS(0)

X

If fault suppression not set, and an illegal address in the SS segment.

X

If fault suppression not set, and a memory address referencing the SS segment is

in a non-canonical form.

General Protection,

#GP(0)

X

If fault suppression not set, and an illegal memory operand effective address in the

CS, DS, ES, FS or GS segments.

X

If fault suppression not set, and the memory address is in a non-canonical form.

X

X

If fault suppression not set, and any part of the operand lies outside the effective

address space from 0 to FFFFH.

Page Fault #PF (fault-

code)

X

X

X

If fault suppression not set, and a page fault.

SIMD Floating-Point

Exception, #XM

X

X

X

X

If an unmasked SIMD floating-point exception, {sae} not set, and CR4.OSXMMEX-

CPT[bit 10] = 1.