2-42 Vol. 2A

INSTRUCTION FORMAT

2.6.11

#UD Equations for EVEX

Instructions encoded using EVEX can face three types of UD conditions: state dependent, opcode independent and

opcode dependent.

2.6.11.1 State Dependent #UD

In general, attempts of execute an instruction, which required OS support for incremental extended state compo-

nent, will #UD if required state components were not enabled by OS. Table 2-37 lists instruction categories with

respect to required processor state components. Attempts to execute a given category of instructions while

enabled states were less than the required bit vector in XCR0 shown in Table 2-37 will cause #UD.

2.6.11.2 Opcode Independent #UD

A number of bit fields in EVEX encoded instruction must obey mode-specific but opcode-independent patterns

listed in Table 2-38.

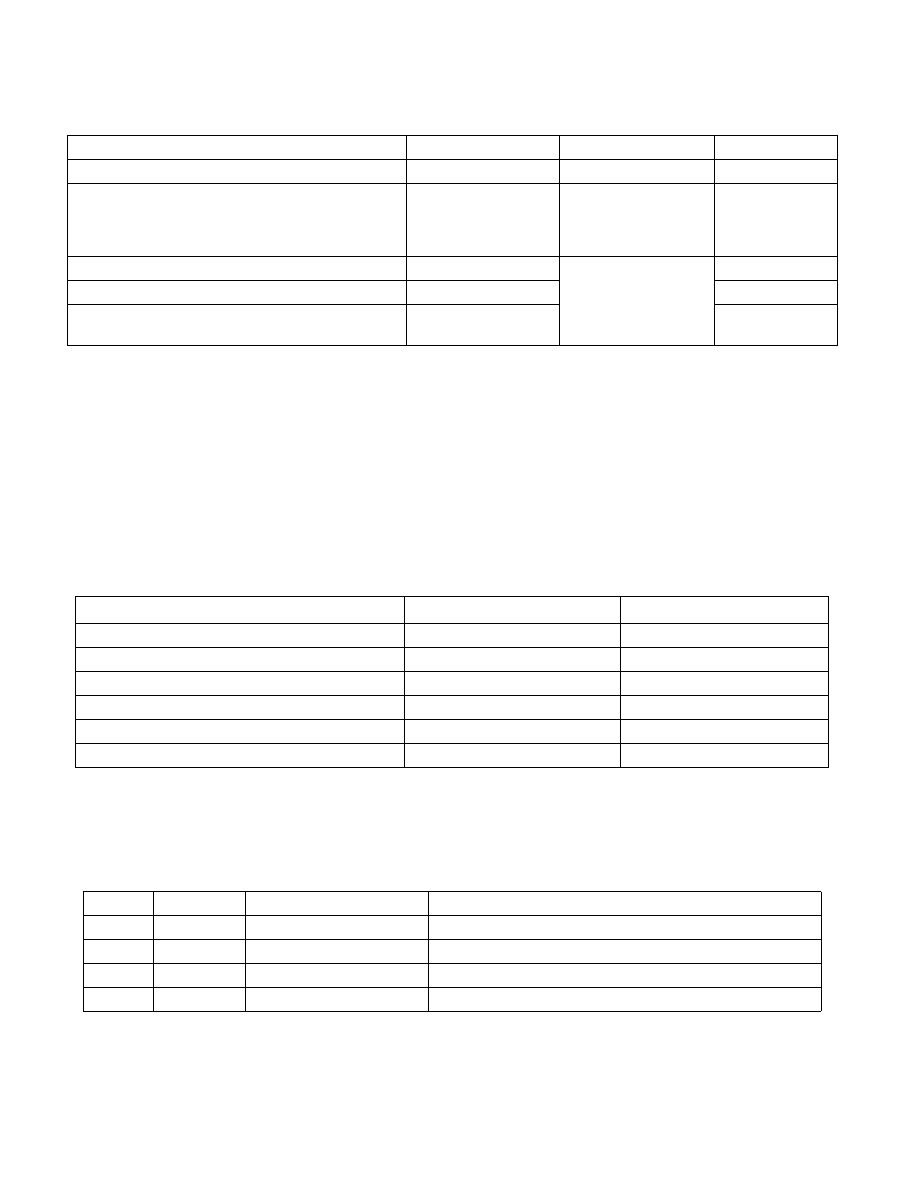

Table 2-36. EVEX Embedded Broadcast/Rounding/SAE and Vector Length on Vector Instructions

Position

P2[4]

P2[6:5]

P2[6:5]

Broadcast/Rounding/SAE Context

EVEX.b

EVEX.L’L

EVEX.RC

Reg-reg, FP Instructions w/ rounding semantic

Enable static rounding

control (SAE implied)

Vector length Implied

(512 bit or scalar)

00b: SAE + RNE

01b: SAE + RD

10b: SAE + RU

11b: SAE + RZ

FP Instructions w/o rounding semantic, can cause #XF

SAE control

00b: 128-bit

01b: 256-bit

10b: 512-bit

11b: Reserved (#UD)

NA

Load+op Instructions w/ memory source

Broadcast Control

NA

Other Instructions (

Explicit Load/Store/Broadcast/Gather/Scatter)

Must be 0 (otherwise

#UD)

NA

Table 2-37. OS XSAVE Enabling Requirements of Instruction Categories

Instruction Categories

Vector Register State Access

Required XCR0 Bit Vector [7:0]

Legacy SIMD prefix encoded Instructions (e.g SSE)

XMM

xxxxxx11b

VEX-encoded instructions operating on YMM

YMM

xxxxx111b

EVEX-encoded 128-bit instructions

ZMM

111xx111b

EVEX-encoded 256-bit instructions

ZMM

111xx111b

EVEX-encoded 512-bit instructions

ZMM

111xx111b

VEX-encoded instructions operating on opmask

k-reg

xx1xxx11b

Table 2-38. Opcode Independent, State Dependent EVEX Bit Fields

Position

Notation

64-bit #UD

Non-64-bit #UD

P[3 : 2]

--

if > 0

if > 0

P[10]

--

if 0

if 0

P[1: 0]

EVEX.mm

if 00b

if 00b

P[7 : 6]

EVEX.RX

None (valid)

None (BOUND if EVEX.RX != 11b)