3-10 Vol. 1

BASIC EXECUTION ENVIRONMENT

3.3.7

Address Calculations in 64-Bit Mode

In most cases, 64-bit mode uses flat address space for code, data, and stacks. In 64-bit mode (if there is no

address-size override), the size of effective address calculations is 64 bits. An effective-address calculation uses a

64-bit base and index registers and sign-extend displacements to 64 bits.

In the flat address space of 64-bit mode, linear addresses are equal to effective addresses because the base

address is zero. In the event that FS or GS segments are used with a non-zero base, this rule does not hold. In 64-

bit mode, the effective address components are added and the effective address is truncated (See for example the

instruction LEA) before adding the full 64-bit segment base. The base is never truncated, regardless of addressing

mode in 64-bit mode.

The instruction pointer is extended to 64 bits to support 64-bit code offsets. The 64-bit instruction pointer is called

the RIP. Table 3-1 shows the relationship between RIP, EIP, and IP.

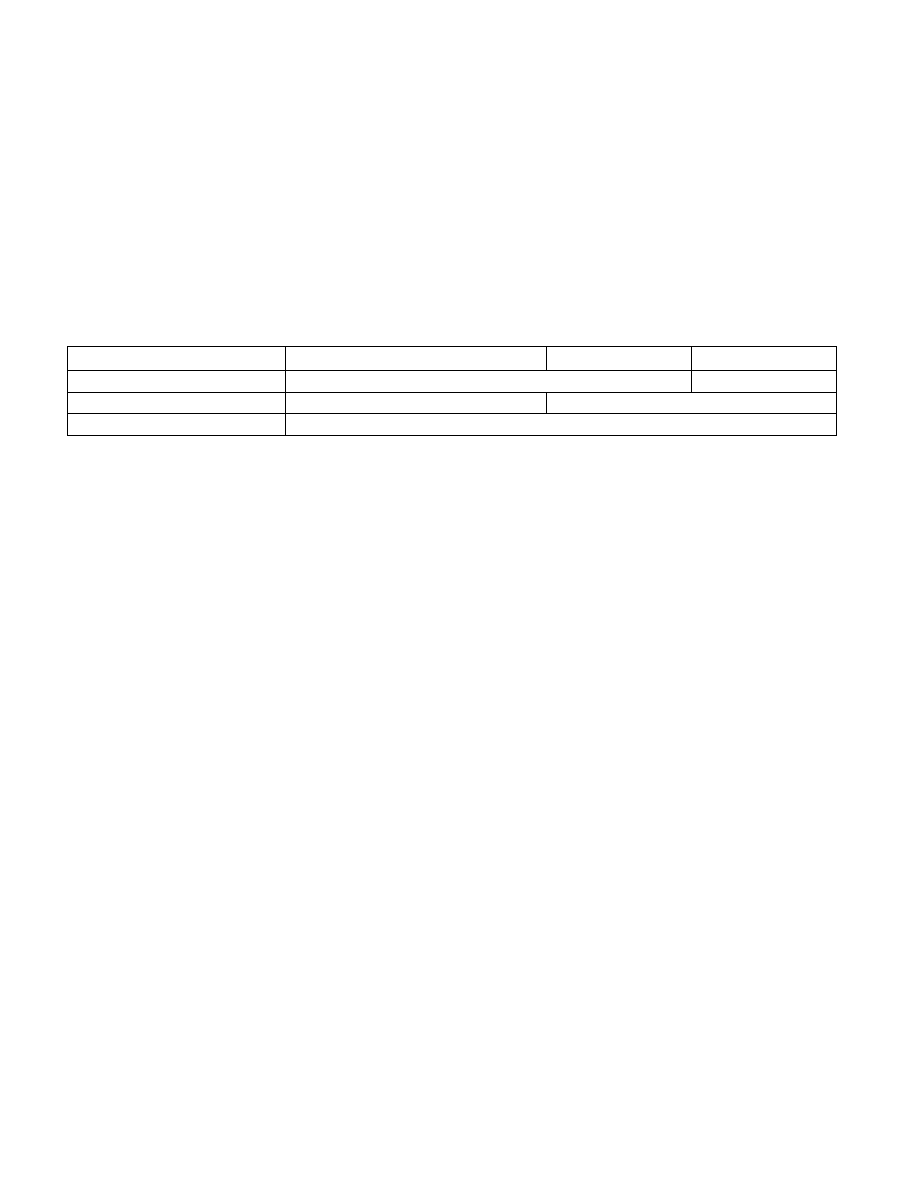

Table 3-1. Instruction Pointer Sizes

Generally, displacements and immediates in 64-bit mode are not extended to 64 bits. They are still limited to 32

bits and sign-extended during effective-address calculations. In 64-bit mode, however, support is provided for 64-

bit displacement and immediate forms of the MOV instruction.

All 16-bit and 32-bit address calculations are zero-extended in IA-32e mode to form 64-bit addresses. Address

calculations are first truncated to the effective address size of the current mode (64-bit mode or compatibility

mode), as overridden by any address-size prefix. The result is then zero-extended to the full 64-bit address width.

Because of this, 16-bit and 32-bit applications running in compatibility mode can access only the low 4 GBytes of

the 64-bit mode effective addresses. Likewise, a 32-bit address generated in 64-bit mode can access only the low

4 GBytes of the 64-bit mode effective addresses.

3.3.7.1

Canonical Addressing

In 64-bit mode, an address is considered to be in canonical form if address bits 63 through to the most-significant

implemented bit by the microarchitecture are set to either all ones or all zeros.

Intel 64 architecture defines a 64-bit linear address. Implementations can support less. The first implementation of

IA-32 processors with Intel 64 architecture supports a 48-bit linear address. This means a canonical address must

have bits 63 through 48 set to zeros or ones (depending on whether bit 47 is a zero or one).

Although implementations may not use all 64 bits of the linear address, they should check bits 63 through the

most-significant implemented bit to see if the address is in canonical form. If a linear-memory reference is not in

canonical form, the implementation should generate an exception. In most cases, a general-protection exception

(#GP) is generated. However, in the case of explicit or implied stack references, a stack fault (#SS) is generated.

Instructions that have implied stack references, by default, use the SS segment register. These include PUSH/POP-

related instructions and instructions using RSP/RBP as base registers. In these cases, the canonical fault is #SS.

If an instruction uses base registers RSP/RBP and uses a segment override prefix to specify a non-SS segment, a

canonical fault generates a #GP (instead of an #SS). In 64-bit mode, only FS and GS segment-overrides are appli-

cable in this situation. Other segment override prefixes (CS, DS, ES and SS) are ignored. Note that this also means

that an SS segment-override applied to a “non-stack” register reference is ignored. Such a sequence still produces

a #GP for a canonical fault (and not an #SS).

3.4 BASIC

PROGRAM

EXECUTION REGISTERS

IA-32 architecture provides 16 basic program execution registers for use in general system and application

programing (see Figure 3-4). These registers can be grouped as follows:

Bits 63:32

Bits 31:16

Bits 15:0

16-bit instruction pointer

Not Modified

IP

32-bit instruction pointer

Zero Extension

EIP

64-bit instruction pointer

RIP