3-8 Vol. 1

BASIC EXECUTION ENVIRONMENT

3.3.2

Paging and Virtual Memory

With the flat or the segmented memory model, linear address space is mapped into the processorŌĆÖs physical

address space either directly or through paging. When using direct mapping (paging disabled), each linear address

has a one-to-one correspondence with a physical address. Linear addresses are sent out on the processorŌĆÖs address

lines without translation.

When using the IA-32 architectureŌĆÖs paging mechanism (paging enabled), linear address space is divided into

pages which are mapped to virtual memory. The pages of virtual memory are then mapped as needed into physical

memory. When an operating system or executive uses paging, the paging mechanism is transparent to an applica-

tion program. All that the application sees is linear address space.

In addition, IA-32 architectureŌĆÖs paging mechanism includes extensions that support:

ŌĆó

Physical Address Extensions (PAE) to address physical address space greater than 4 GBytes.

ŌĆó

Page Size Extensions (PSE) to map linear address to physical address in 4-MBytes pages.

See also: Chapter 3, ŌĆ£Protected-Mode Memory Management,ŌĆØ in the Intel┬« 64 and IA-32 Architectures Software

DeveloperŌĆÖs Manual, Volume 3A.

3.3.3

Memory Organization in 64-Bit Mode

Intel 64 architecture supports physical address space greater than 64 GBytes; the actual physical address size of

IA-32 processors is implementation specific. In 64-bit mode, there is architectural support for 64-bit linear address

space. However, processors supporting Intel 64 architecture may implement less than 64-bits (see Section

3.3.7.1). The linear address space is mapped into the processor physical address space through the PAE paging

mechanism.

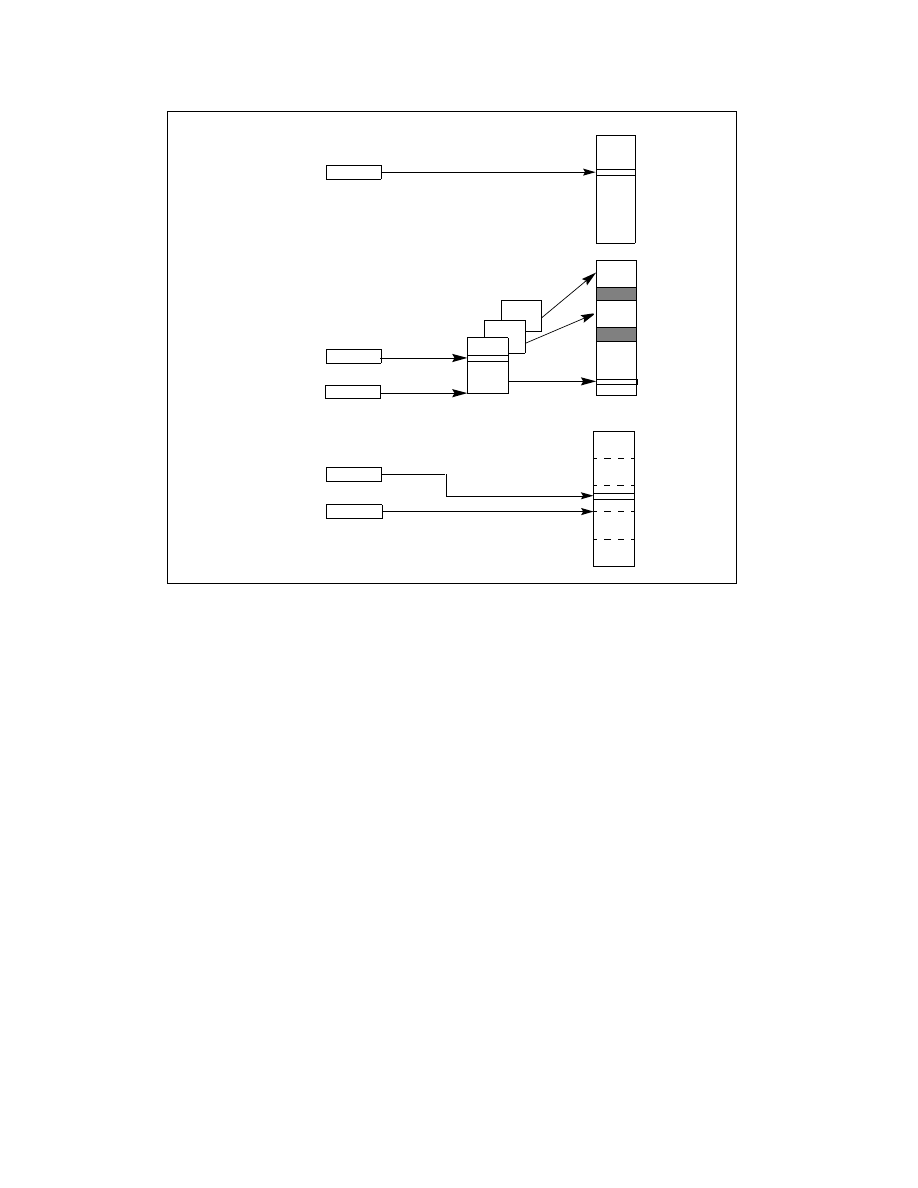

Figure 3-3. Three Memory Management Models

Linear Address

Flat Model

Linear

Address

Space*

Segment Selector

Offset

Segment Selector

Segmented Model

Real-Address Mode Model

Linear Address

Logical

Offset (effective address)

Space Divided

Into Equal

Sized Segments

Address

Logical

Address

Linear

Address

Space*

Segments

* The linear address space

can be paged when using the

flat or segmented model.