14-20 Vol. 1

PROGRAMMING WITH AVX, FMA AND AVX2

14.4.1

Detection of F16C Instructions

Application using float 16 instruction must follow a detection sequence similar to AVX to ensure:

•

The OS has enabled YMM state management support,

•

The processor support AVX as indicated by the CPUID feature flag, i.e. CPUID.01H:ECX.AVX[bit 28] = 1.

•

The processor support 16-bit floating-point conversion instructions via a CPUID feature flag

(CPUID.01H:ECX.F16C[bit 29] = 1).

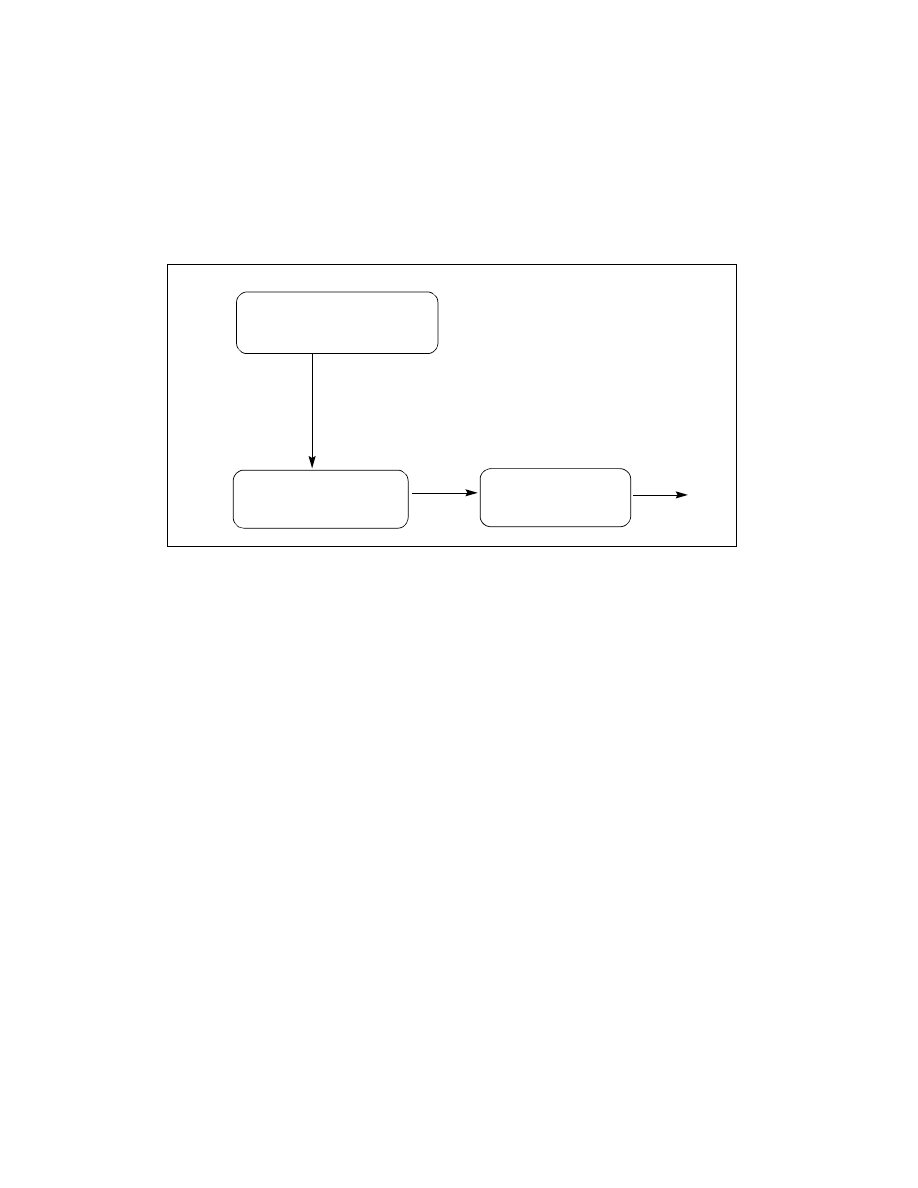

Application detection of Float-16 conversion instructions follow the general procedural flow in Figure 14-3.

----------------------------------------------------------------------------------------

INT supports_f16c()

{

; result in eax

mov eax, 1

cpuid

and ecx, 038000000H

cmp ecx, 038000000H; check OSXSAVE, AVX, F16C feature flags

jne not_supported

; processor supports AVX,F16C instructions and XGETBV is enabled by OS

mov ecx, 0; specify 0 for XCR0 register

XGETBV; result in EDX:EAX

and eax, 06H

cmp eax, 06H; check OS has enabled both XMM and YMM state support

jne not_supported

mov eax, 1

jmp done

NOT_SUPPORTED:

mov eax, 0

done:

}

-------------------------------------------------------------------------------

Figure 14-3. General Procedural Flow of Application Detection of Float-16

Implied HW support for

Check enabled YMM state in

XCR0 via XGETBV

Check feature flags

for AVX and F16C

Check feature flag

CPUID.1H:ECX.OSXSAVE = 1?

OS provides processor

extended state management

State

ok to use

XSAVE, XRSTOR, XGETBV, XCR0

enabled

Instructions

Yes