14-14 Vol. 1

PROGRAMMING WITH AVX, FMA AND AVX2

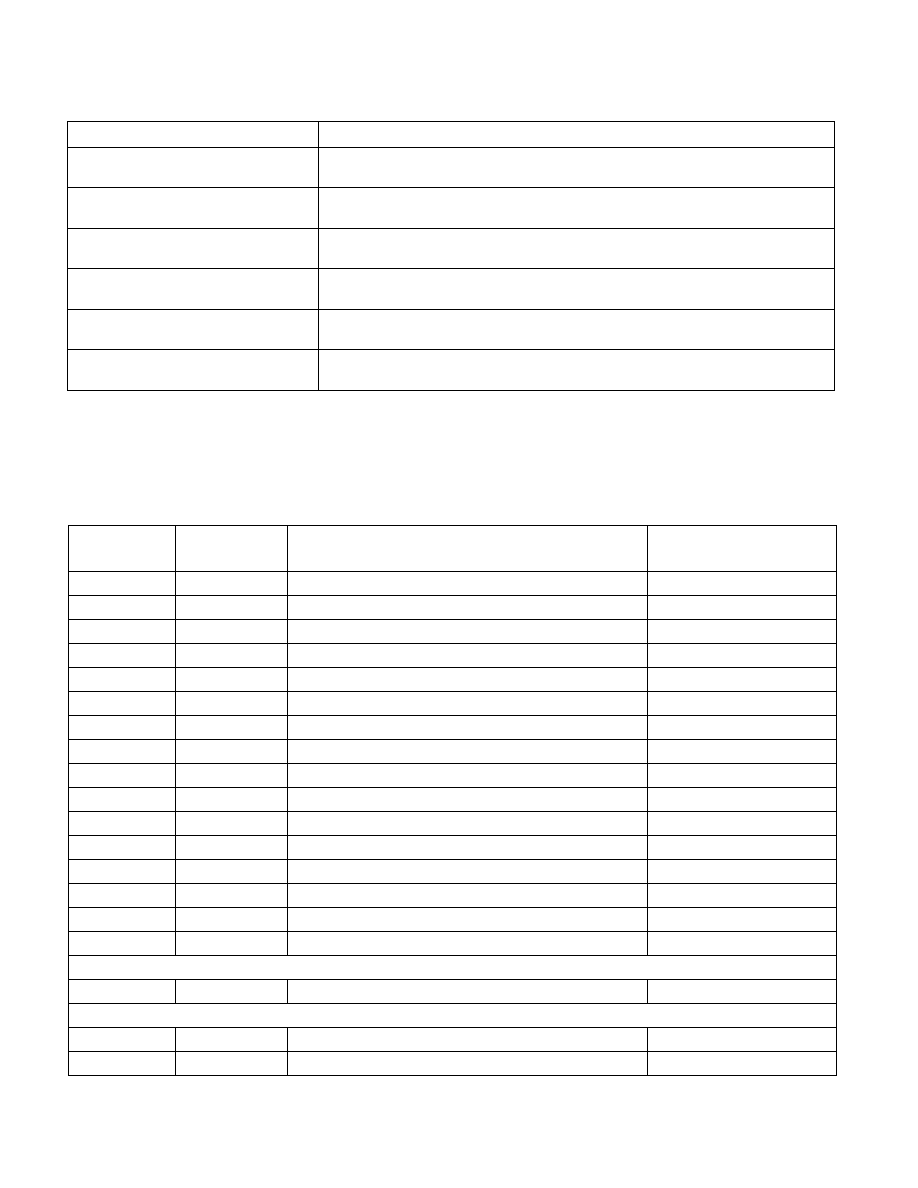

The 128-bit data processing instructions in AVX cover floating-point and integer data movement primitives. Legacy

SIMD non-arithmetic ISA promoted to VEX-256 encoding also support VEX-128 encoding (see Table 14-3). Table

14-7 lists the state of promotion of the remaining legacy SIMD non-arithmetic ISA to VEX-128 encoding.

VPERMILPD xmm1, xmm2, xmm3/m128

Permute Double-Precision Floating-Point values in xmm2 using controls from xmm3/mem

and store result in xmm1

VPERMILPD xmm1, xmm2/m128, imm8

Permute Double-Precision Floating-Point values in xmm2/mem using controls from imm8

and store result in xmm1

VPERMILPS xmm1, xmm2, xmm3/m128

Permute Single-Precision Floating-Point values in xmm2 using controls from xmm3/mem

and store result in xmm1

VPERMILPS xmm1, xmm2/m128, imm8

Permute Single-Precision Floating-Point values in xmm2/mem using controls from imm8

and store result in xmm1

VTESTPS xmm1, xmm2/m128

Set ZF if xmm2/mem AND xmm1 result is all 0s in packed single-precision sign bits. Set

CF if xmm2/mem AND NOT xmm1 result is all 0s in packed single-precision sign bits.

VTESTPD xmm1, xmm2/m128

Set ZF if xmm2/mem AND xmm1 result is all 0s in packed single precision sign bits. Set CF

if xmm2/mem AND NOT xmm1 result is all 0s in packed double-precision sign bits.

Table 14-7. Promotion of Legacy SIMD ISA to 128-bit Non-Arithmetic AVX instruction

VEX.256

Encoding

VEX.128

Encoding

Instruction

Reason Not Promoted

no

no

MOVQ2DQ, MOVDQ2Q

MMX

no

yes

LDMXCSR, STMXCSR

no

yes

MOVSS, MOVSD, CMPSS, CMPSD

scalar

no

yes

MOVHPS, MOVHPD

Note 1

no

yes

MOVLPS, MOVLPD

Note 1

no

yes

MOVLHPS, MOVHLPS

Redundant with VPERMILPS

no

yes

MOVQ, MOVD

scalar

no

yes

PACKUSWB, PACKSSDW, PACKSSWB

VI

no

yes

PUNPCKHBW, PUNPCKHWD

VI

no

yes

PUNPCKLBW, PUNPCKLWD

VI

no

yes

PUNPCKHDQ, PUNPCKLDQ

VI

no

yes

PUNPCKLQDQ, PUNPCKHQDQ

VI

no

yes

PSHUFHW, PSHUFLW, PSHUFD

VI

no

yes

PMOVMSKB, MASKMOVDQU

VI

no

yes

PAND, PANDN, POR, PXOR

VI

no

yes

PINSRW, PEXTRW,

VI

CPUID.SSSE3

no

yes

PALIGNR, PSHUFB

VI

CPUID.SSE4_1

no

yes

EXTRACTPS, INSERTPS

Note 3

no

yes

PACKUSDW, PCMPEQQ

VI

Table 14-6. 128-bit AVX Instruction Enhancement

Instruction

Description