11-20 Vol. 1

PROGRAMMING WITH INTEL® STREAMING SIMD EXTENSIONS 2 (INTEL® SSE2)

If the processor attempts to execute an unsupported SSE or SSE2 instruction, the processor will generate an

invalid-opcode exception (#UD). If an operating system did not provide adequate system level support for SSE,

executing an SSE or SSE2 instructions can also generate #UD.

11.6.3

Checking for the DAZ Flag in the MXCSR Register

The denormals-are-zero flag in the MXCSR register is available in most of the Pentium 4 processors and in the Intel

Xeon processor, with the exception of some early steppings. To check for the presence of the DAZ flag in the MXCSR

register, do the following:

1. Establish a 512-byte FXSAVE area in memory.

2. Clear the FXSAVE area to all 0s.

3. Execute the FXSAVE instruction, using the address of the first byte of the cleared FXSAVE area as a source

operand. See “FXSAVE—Save x87 FPU, MMX, SSE, and SSE2 State” in Chapter 3 of the Intel® 64 and IA-32

Architectures Software Developer’s Manual, Volume 2A, for a description of the FXSAVE instruction and the

layout of the FXSAVE image.

4. Check the value in the MXCSR_MASK field in the FXSAVE image (bytes 28 through 31).

— If the value of the MXCSR_MASK field is 00000000H, the DAZ flag and denormals-are-zero mode are not

supported.

— If the value of the MXCSR_MASK field is non-zero and bit 6 is set, the DAZ flag and denormals-are-zero

mode are supported.

If the DAZ flag is not supported, then it is a reserved bit and attempting to write a 1 to it will cause a general-

protection exception (#GP). See Section 11.6.6, “Guidelines for Writing to the MXCSR Register,” for general guide-

lines for preventing general-protection exceptions when writing to the MXCSR register.

11.6.4

Initialization of SSE/SSE2 Extensions

The SSE and SSE2 state is contained in the XMM and MXCSR registers. Upon a hardware reset of the processor, this

state is initialized as follows (see Table 11-2):

•

All SIMD floating-point exceptions are masked (bits 7 through 12 of the MXCSR register is set to 1).

•

All SIMD floating-point exception flags are cleared (bits 0 through 5 of the MXCSR register is set to 0).

•

The rounding control is set to round-nearest (bits 13 and 14 of the MXCSR register are set to 00B).

•

The flush-to-zero mode is disabled (bit 15 of the MXCSR register is set to 0).

•

The denormals-are-zeros mode is disabled (bit 6 of the MXCSR register is set to 0). If the denormals-are-zeros

mode is not supported, this bit is reserved and will be set to 0 on initialization.

•

Each of the XMM registers is cleared (set to all zeros).

If the processor is reset by asserting the INIT# pin, the SSE and SSE2 state is not changed.

11.6.5

Saving and Restoring the SSE/SSE2 State

The FXSAVE instruction saves the x87 FPU, MMX, SSE and SSE2 states (which includes the contents of eight XMM

registers and the MXCSR registers) in a 512-byte block of memory. The FXRSTOR instruction restores the saved

SSE and SSE2 state from memory. See the FXSAVE instruction in Chapter 3 of the Intel® 64 and IA-32 Architec-

tures Software Developer’s Manual, Volume 2A, for the layout of the 512-byte state block.

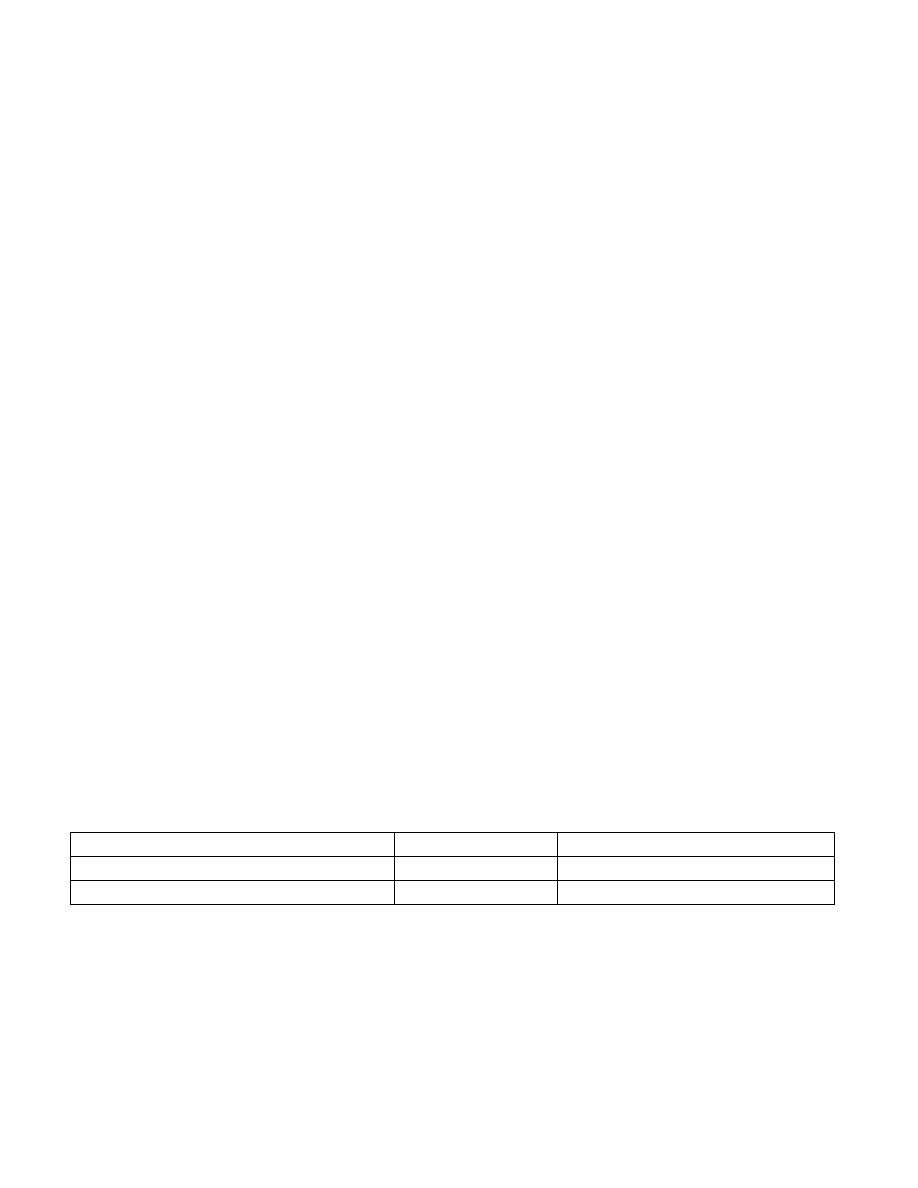

Table 11-2. SSE and SSE2 State Following a Power-up/Reset or INIT

Registers

Power-Up or Reset

INIT

XMM0 through XMM7

+0.0

Unchanged

MXCSR

1F80H

Unchanged