8-20 Vol. 1

PROGRAMMING WITH THE X87 FPU

If an unordered condition is detected (one or both of the values are NaNs or in an undefined format), a floating-

point invalid-operation exception is generated.

The pop versions of the instruction pop the x87 FPU register stack once or twice after the comparison operation is

complete.

The FUCOM, FUCOMP, and FUCOMPP instructions operate the same as the FCOM, FCOMP, and FCOMPP instructions.

The only difference is that with the FUCOM, FUCOMP, and FUCOMPP instructions, if an unordered condition is

detected because one or both of the operands are QNaNs, the floating-point invalid-operation exception is not

generated.

The FICOM and FICOMP instructions also operate the same as the FCOM and FCOMP instructions, except that the

source operand is an integer value in memory. The integer value is automatically converted into an double

extended-precision floating-point value prior to making the comparison. The FICOMP instruction pops the x87 FPU

register stack following the comparison operation.

The FTST instruction performs the same operation as the FCOM instruction, except that the value in register ST(0)

is always compared with the value 0.0.

The FCOMI and FCOMIP instructions were introduced into the IA-32 architecture in the P6 family processors. They

perform the same comparison as the FCOM and FCOMP instructions, except that they set the status flags (ZF, PF,

and CF) in the EFLAGS register to indicate the results of the comparison (see Table 8-7) instead of the x87 FPU

condition code flags. The FCOMI and FCOMIP instructions allow condition branch instructions (Jcc) to be executed

directly from the results of their comparison.

Software can check if the FCOMI and FCOMIP instructions are supported by checking the processor’s feature infor-

mation with the CPUID instruction.

The FUCOMI and FUCOMIP instructions operate the same as the FCOMI and FCOMIP instructions, except that they

do not generate a floating-point invalid-operation exception if the unordered condition is the result of one or both

of the operands being a QNaN. The FCOMIP and FUCOMIP instructions pop the x87 FPU register stack following the

comparison operation.

The FXAM instruction determines the classification of the floating-point value in the ST(0) register (that is, whether

the value is zero, a denormal number, a normal finite number, ∞, a NaN, or an unsupported format) or that the

register is empty. It sets the x87 FPU condition code flags to indicate the classification (see “FXAM—Examine” in

Chapter 3, “Instruction Set Reference, A-L,” of the Intel® 64 and IA-32 Architectures Software Developer’s Manual,

Volume 2A). It also sets the C1 flag to indicate the sign of the value.

8.3.6.1

Branching on the x87 FPU Condition Codes

The processor does not offer any control-flow instructions that branch on the setting of the condition code flags

(C0, C2, and C3) in the x87 FPU status word. To branch on the state of these flags, the x87 FPU status word must

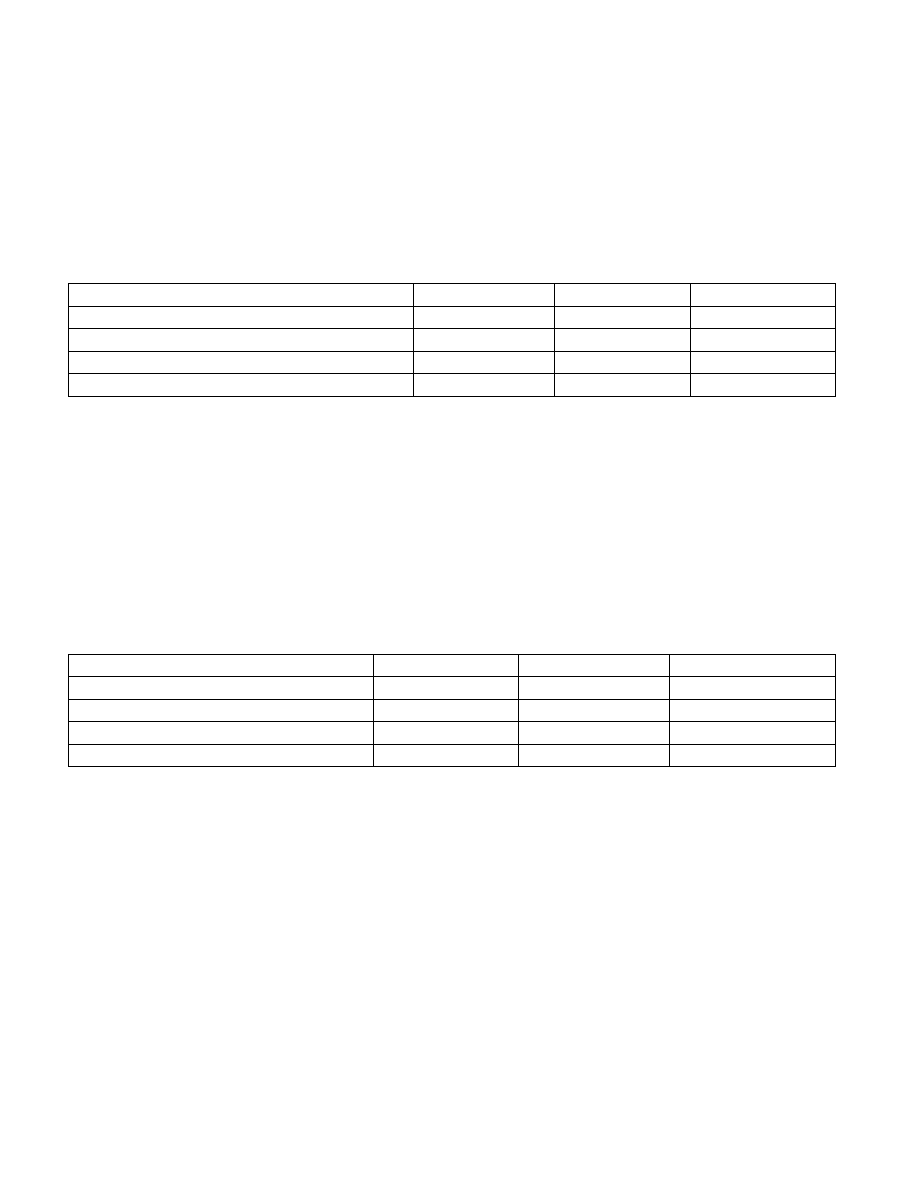

Table 8-6. Setting of x87 FPU Condition Code Flags for Floating-Point Number Comparisons

Condition

C3

C2

C0

ST(0) > Source Operand

0

0

0

ST(0) < Source Operand

0

0

1

ST(0) = Source Operand

1

0

0

Unordered

1

1

1

Table 8-7. Setting of EFLAGS Status Flags for Floating-Point Number Comparisons

Comparison Results

ZF

PF

CF

ST0 > ST(i)

0

0

0

ST0 < ST(i)

0

0

1

ST0 = ST(i)

1

0

0

Unordered

1

1

1