Vol. 1 8-17

PROGRAMMING WITH THE X87 FPU

The FST (store floating point) and FIST (store integer) instructions store the value in register ST(0) in memory in

the destination format (floating point or integer, respectively). Again, the format conversion is carried out automat-

ically.

The FSTP (store floating point and pop), FISTP (store integer and pop), and FBSTP (store packed decimal and pop)

instructions store the value in the ST(0) registers into memory in the destination format (floating point, integer, or

packed BCD), then performs a pop operation on the register stack. A pop operation causes the ST(0) register to be

marked empty and the stack pointer (TOP) in the x87 FPU control work to be incremented by 1. The FSTP instruc-

tion can also be used to copy the value in the ST(0) register to another x87 FPU register [ST(i)].

The FXCH (exchange register contents) instruction exchanges the value in a selected register in the stack [ST(i)]

with the value in ST(0).

The FCMOVcc (conditional move) instructions move the value in a selected register in the stack [ST(i)] to register

ST(0) if a condition specified with a condition code (cc) is satisfied (see Table 8-5). The condition being tested for

is represented by the status flags in the EFLAGS register. The condition code mnemonics are appended to the

letters “FCMOV” to form the mnemonic for a FCMOVcc instruction.

Like the CMOVcc instructions, the FCMOVcc instructions are useful for optimizing small IF constructions. They also

help eliminate branching overhead for IF operations and the possibility of branch mispredictions by the processor.

Software can check if the FCMOVcc instructions are supported by checking the processor’s feature information with

the CPUID instruction.

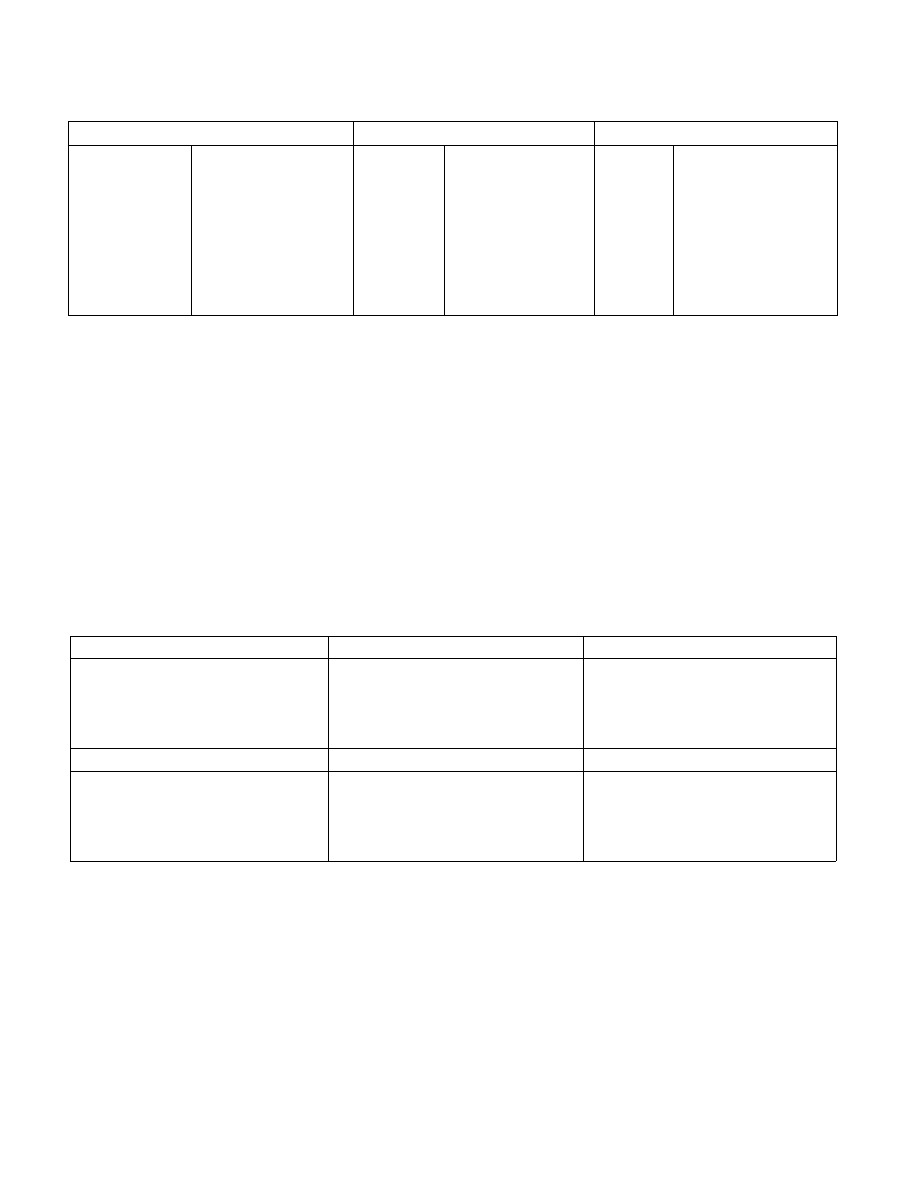

Table 8-4. Data Transfer Instructions

Floating Point

Integer

Packed Decimal

FLD

Load Floating Point

FILD

Load Integer

FBLD

Load Packed

Decimal

FST

Store Floating Point

FIST

Store Integer

FSTP

Store Floating Point and

Pop

FISTP

Store Integer

and Pop

FBSTP

Store Packed

Decimal and Pop

FXCH Exchange

Register

Contents

FCMOVcc

Conditional Move

Table 8-5. Floating-Point Conditional Move Instructions

Instruction Mnemonic

Status Flag States

Condition Description

FCMOVB

CF=1

Below

FCMOVNB

CF=0

Not below

FCMOVE

ZF=1

Equal

FCMOVNE

ZF=0

Not equal

Instruction Mnemonic

Status Flag States

Condition Description

FCMOVBE

CF=1 or ZF=1

Below or equal

FCMOVNBE

CF=0 or ZF=0

Not below nor equal

FCMOVU

PF=1

Unordered

FCMOVNU

PF=0

Not unordered