Vol. 1 8-7

PROGRAMMING WITH THE X87 FPU

The new mechanism is available beginning with the P6 family processors. Using this mechanism, the new floating-

point compare and set EFLAGS instructions (FCOMI, FCOMIP, FUCOMI, and FUCOMIP) compare two floating-point

values and set the ZF, PF, and CF flags in the EFLAGS register directly. A single instruction thus replaces the three

instructions required by the old mechanism.

Note also that the FCMOVcc instructions (also new in the P6 family processors) allow conditional moves of floating-

point values (values in the x87 FPU data registers) based on the setting of the status flags (ZF, PF, and CF) in the

EFLAGS register. These instructions eliminate the need for an IF statement to perform conditional moves of

floating-point values.

8.1.5

x87 FPU Control Word

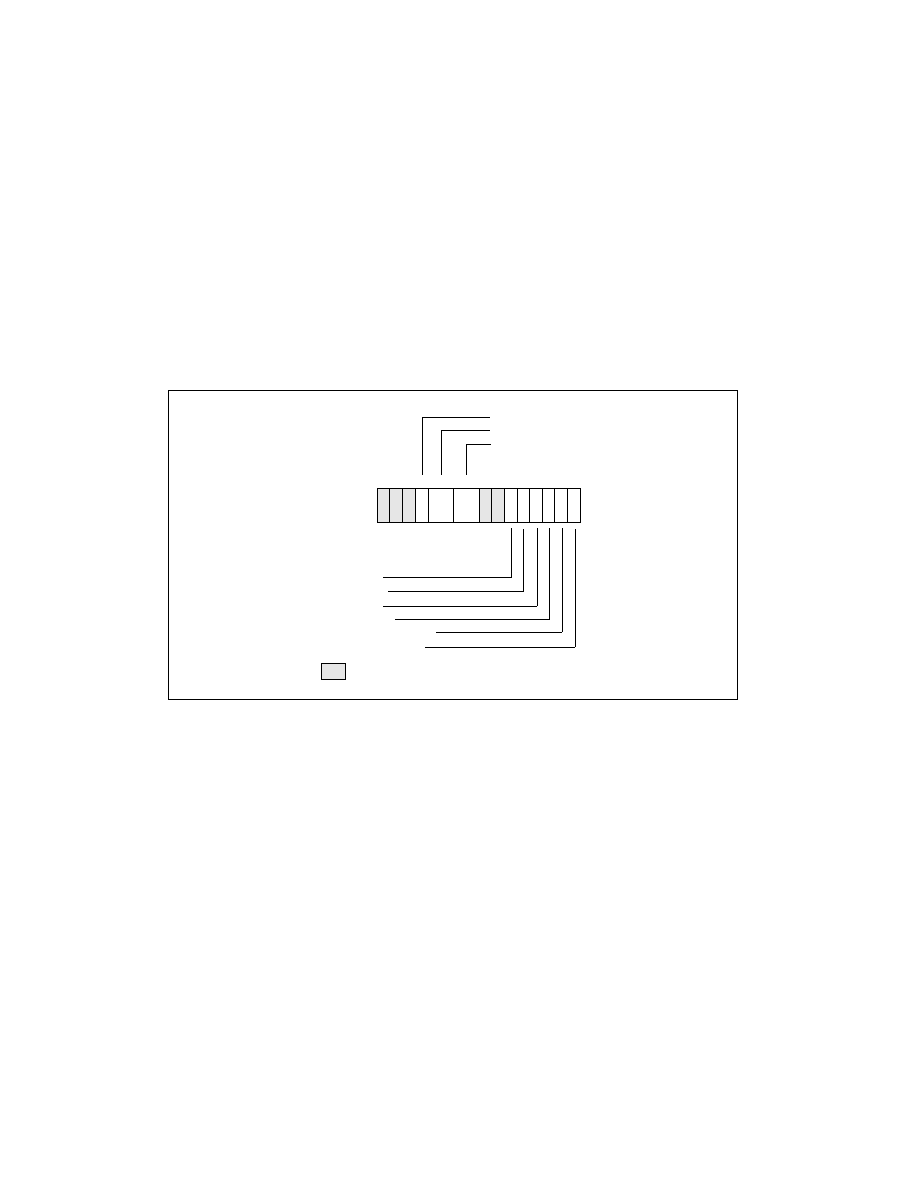

The 16-bit x87 FPU control word (see Figure 8-6) controls the precision of the x87 FPU and rounding method used.

It also contains the x87 FPU floating-point exception mask bits. The control word is cached in the x87 FPU control

register. The contents of this register can be loaded with the FLDCW instruction and stored in memory with the

FSTCW/FNSTCW instructions.

When the x87 FPU is initialized with either an FINIT/FNINIT or FSAVE/FNSAVE instruction, the x87 FPU control

word is set to 037FH, which masks all floating-point exceptions, sets rounding to nearest, and sets the x87 FPU

precision to 64 bits.

8.1.5.1

x87 FPU Floating-Point Exception Mask Bits

The exception-flag mask bits (bits 0 through 5 of the x87 FPU control word) mask the 6 floating-point exception

flags in the x87 FPU status word. When one of these mask bits is set, its corresponding x87 FPU floating-point

exception is blocked from being generated.

8.1.5.2

Precision Control Field

The precision-control (PC) field (bits 8 and 9 of the x87 FPU control word) determines the precision (64, 53, or 24

bits) of floating-point calculations made by the x87 FPU (see Table 8-2). The default precision is double extended

precision, which uses the full 64-bit significand available with the double extended-precision floating-point format

of the x87 FPU data registers. This setting is best suited for most applications, because it allows applications to take

full advantage of the maximum precision available with the x87 FPU data registers.

Figure 8-6. x87 FPU Control Word

15

13

14

12 11 10 9 8 7 6 5 4 3 2 1 0

X

I

M

P

M

O

M

U

M

Z

M

D

M

RC

PC

Infinity Control

Rounding Control

Precision Control

Exception Masks

Precision

Underflow

Overflow

Zero Divide

Denormal Operand

Invalid Operation

Reserved