8-6 Vol. 1

PROGRAMMING WITH THE X87 FPU

8.1.3.4

Stack Fault Flag

The stack fault flag (bit 6 of the x87 FPU status word) indicates that stack overflow or stack underflow has occurred

with data in the x87 FPU data register stack. The x87 FPU explicitly sets the SF flag when it detects a stack overflow

or underflow condition, but it does not explicitly clear the flag when it detects an invalid-arithmetic-operand condi-

tion.

When this flag is set, the condition code flag C1 indicates the nature of the fault: overflow (C1 = 1) and under-

flow (C1 = 0). The SF flag is a “sticky” flag, meaning that after it is set, the processor does not clear it until it is

explicitly instructed to do so (for example, by an FINIT/FNINIT, FCLEX/FNCLEX, or FSAVE/FNSAVE instruction).

See Section 8.1.7, “x87 FPU Tag Word,” for more information on x87 FPU stack faults.

8.1.4

Branching and Conditional Moves on Condition Codes

The x87 FPU (beginning with the P6 family processors) supports two mechanisms for branching and performing

conditional moves according to comparisons of two floating-point values. These mechanism are referred to here as

the “old mechanism” and the “new mechanism.”

The old mechanism is available in x87 FPU’s prior to the P6 family processors and in P6 family processors. This

mechanism uses the floating-point compare instructions (FCOM, FCOMP, FCOMPP, FTST, FUCOMPP, FICOM, and

FICOMP) to compare two floating-point values and set the condition code flags (C0 through C3) according to the

results. The contents of the condition code flags are then copied into the status flags of the EFLAGS register using

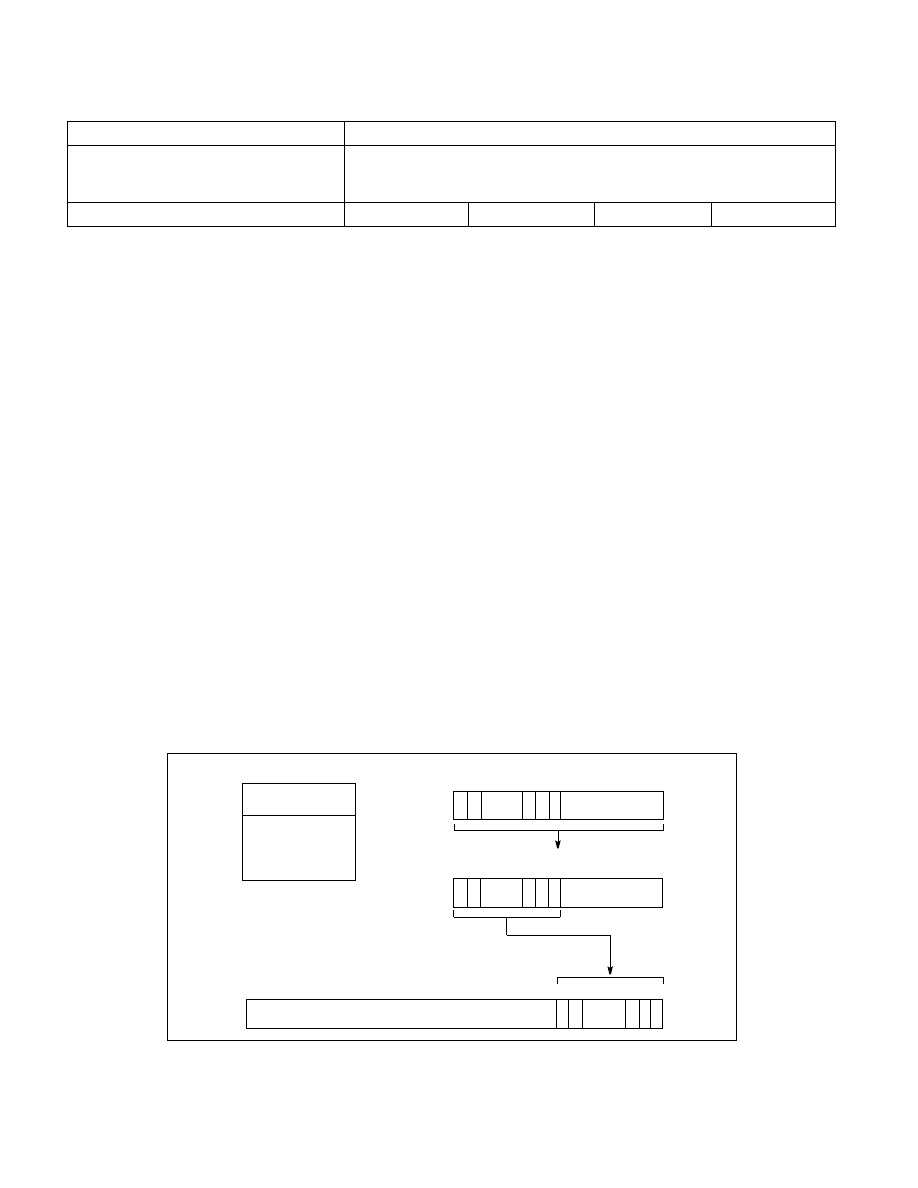

a two step process (see Figure 8-5):

1. The FSTSW AX instruction moves the x87 FPU status word into the AX register.

2. The SAHF instruction copies the upper 8 bits of the AX register, which includes the condition code flags, into the

lower 8 bits of the EFLAGS register.

When the condition code flags have been loaded into the EFLAGS register, conditional jumps or conditional moves

can be performed based on the new settings of the status flags in the EFLAGS register.

FLDENV, FRSTOR

Each bit loaded from memory

FFREE, FLDCW, FCLEX/FNCLEX, FNOP,

FSTCW/FNSTCW, FSTENV/FNSTENV,

FSTSW/FNSTSW,

Undefined

FINIT/FNINIT, FSAVE/FNSAVE

0

0

0

0

Figure 8-5. Moving the Condition Codes to the EFLAGS Register

Table 8-1. Condition Code Interpretation (Contd.)

0

Condition

Code

Status

Flag

C0

C1

C2

C3

CF

(none)

PF

ZF

C

F

1

P

F

Z

F

7

31

EFLAGS Register

0

C

2

C

1

C

3

AX Register

0

C

15

0

C

2

C

1

C

3

x87 FPU Status Word

0

C

15

FSTSW AX Instruction

SAHF Instruction