7-16 Vol. 1

PROGRAMMING WITH GENERAL-PURPOSE INSTRUCTIONS

The destination operand specifies a relative address (a signed offset with respect to the address in the EIP register)

that points to an instruction in the current code segment. The Jcc instructions do not support far transfers;

however, far transfers can be accomplished with a combination of a Jcc and a JMP instruction (see ÔÇťJccÔÇöJump if

Condition Is MetÔÇŁ in Chapter 3, ÔÇťInstruction Set Reference, A-L,ÔÇŁ of the Intel┬« 64 and IA-32 Architectures Software

DeveloperÔÇÖs Manual, Volume 2A).

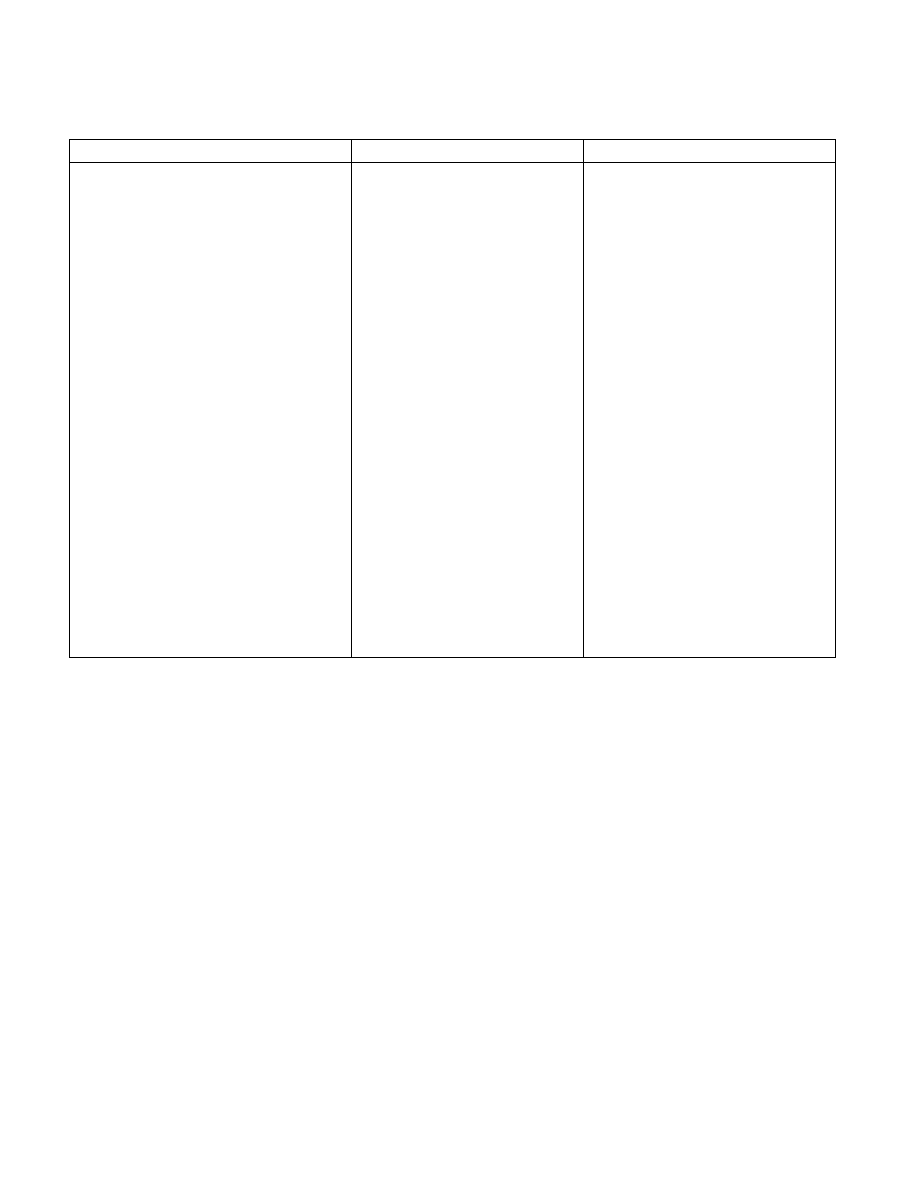

Table 7-4 shows the mnemonics for the Jcc instructions and the conditions being tested for each instruction. The

condition code mnemonics are appended to the letter ÔÇťJÔÇŁ to form the mnemonic for a Jcc instruction. The instruc-

tions are divided into two groups: unsigned and signed conditional jumps. These groups correspond to the results

of operations performed on unsigned and signed integers respectively. Those instructions listed as pairs (for

example, JA/JNBE) are alternate names for the same instruction. Assemblers provide alternate names to make it

easier to read program listings.

The JCXZ and JECXZ instructions test the CX and ECX registers, respectively, instead of one or more status flags.

See ÔÇťJump if zero instructionsÔÇŁ on page 7-17 for more information about these instructions.

Loop instructions ÔÇö The LOOP, LOOPE (loop while equal), LOOPZ (loop while zero), LOOPNE (loop while not

equal), and LOOPNZ (loop while not zero) instructions are conditional jump instructions that use the value of the

ECX register as a count for the number of times to execute a loop. All the loop instructions decrement the count in

the ECX register each time they are executed and terminate a loop when zero is reached. The LOOPE, LOOPZ,

LOOPNE, and LOOPNZ instructions also accept the ZF flag as a condition for terminating the loop before the count

reaches zero.

The LOOP instruction decrements the contents of the ECX register (or the CX register, if the address-size attribute

is 16), then tests the register for the loop-termination condition. If the count in the ECX register is non-zero,

program control is transferred to the instruction address specified by the destination operand. The destination

Table 7-4. Conditional Jump Instructions

Instruction Mnemonic

Condition (Flag States)

Description

Unsigned Conditional Jumps

JA/JNBE

(CF or ZF) = 0

Above/not below or equal

JAE/JNB

CF = 0

Above or equal/not below

JB/JNAE

CF = 1

Below/not above or equal

JBE/JNA

(CF or ZF) = 1

Below or equal/not above

JC

CF = 1

Carry

JE/JZ

ZF = 1

Equal/zero

JNC

CF = 0

Not carry

JNE/JNZ

ZF = 0

Not equal/not zero

JNP/JPO

PF = 0

Not parity/parity odd

JP/JPE

PF = 1

Parity/parity even

JCXZ

CX = 0

Register CX is zero

JECXZ

ECX = 0

Register ECX is zero

Signed Conditional Jumps

JG/JNLE

((SF xor OF) or ZF) = 0

Greater/not less or equal

JGE/JNL

(SF xor OF) = 0

Greater or equal/not less

JL/JNGE

(SF xor OF) = 1

Less/not greater or equal

JLE/JNG

((SF xor OF) or ZF) = 1

Less or equal/not greater

JNO

OF = 0

Not overflow

JNS

SF = 0

Not sign (non-negative)

JO

OF = 1

Overflow

JS

SF = 1

Sign (negative)