Vol. 3B 20-3

8086 EMULATION

The IA-32 processors beginning with the Intel386 processor can generate 32-bit offsets using an address override

prefix; however, in real-address mode, the value of a 32-bit offset may not exceed FFFFH without causing an

exception.

For full compatibility with Intel 286 real-address mode, pseudo-protection faults (interrupt 12 or 13) occur if a 32-

bit offset is generated outside the range 0 through FFFFH.

20.1.2

Registers Supported in Real-Address Mode

The register set available in real-address mode includes all the registers defined for the 8086 processor plus the

new registers introduced in later IA-32 processors, such as the FS and GS segment registers, the debug registers,

the control registers, and the floating-point unit registers. The 32-bit operand prefix allows a real-address mode

program to use the 32-bit general-purpose registers (EAX, EBX, ECX, EDX, ESP, EBP, ESI, and EDI).

20.1.3

Instructions Supported in Real-Address Mode

The following instructions make up the core instruction set for the 8086 processor. If backwards compatibility to

the Intel 286 and Intel 8086 processors is required, only these instructions should be used in a new program

written to run in real-address mode.

•

Move (MOV) instructions that move operands between general-purpose registers, segment registers, and

between memory and general-purpose registers.

•

The exchange (XCHG) instruction.

•

Load segment register instructions LDS and LES.

•

Arithmetic instructions ADD, ADC, SUB, SBB, MUL, IMUL, DIV, IDIV, INC, DEC, CMP, and NEG.

•

Logical instructions AND, OR, XOR, and NOT.

•

Decimal instructions DAA, DAS, AAA, AAS, AAM, and AAD.

•

Stack instructions PUSH and POP (to general-purpose registers and segment registers).

•

Type conversion instructions CWD, CDQ, CBW, and CWDE.

•

Shift and rotate instructions SAL, SHL, SHR, SAR, ROL, ROR, RCL, and RCR.

•

TEST instruction.

•

Control instructions JMP, Jcc, CALL, RET, LOOP, LOOPE, and LOOPNE.

•

Interrupt instructions INT n, INTO, and IRET.

•

EFLAGS control instructions STC, CLC, CMC, CLD, STD, LAHF, SAHF, PUSHF, and POPF.

•

I/O instructions IN, INS, OUT, and OUTS.

•

Load effective address (LEA) instruction, and translate (XLATB) instruction.

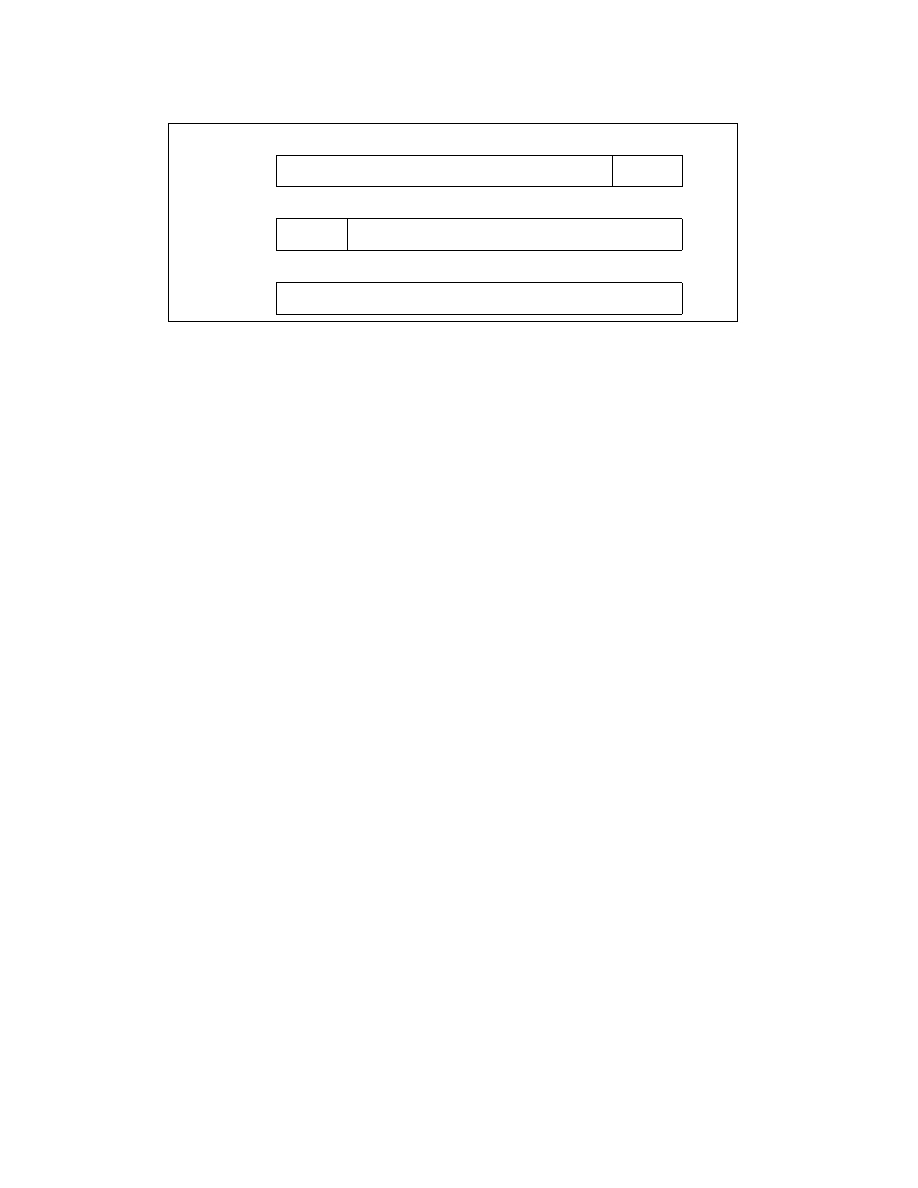

Figure 20-1. Real-Address Mode Address Translation

19

0

16-bit Segment Selector

3

0 0 0 0

Base

19

0

16-bit Effective Address

15

0 0 0 0

Offset

0

20-bit Linear Address

Linear

Address

+

=

4

16

19