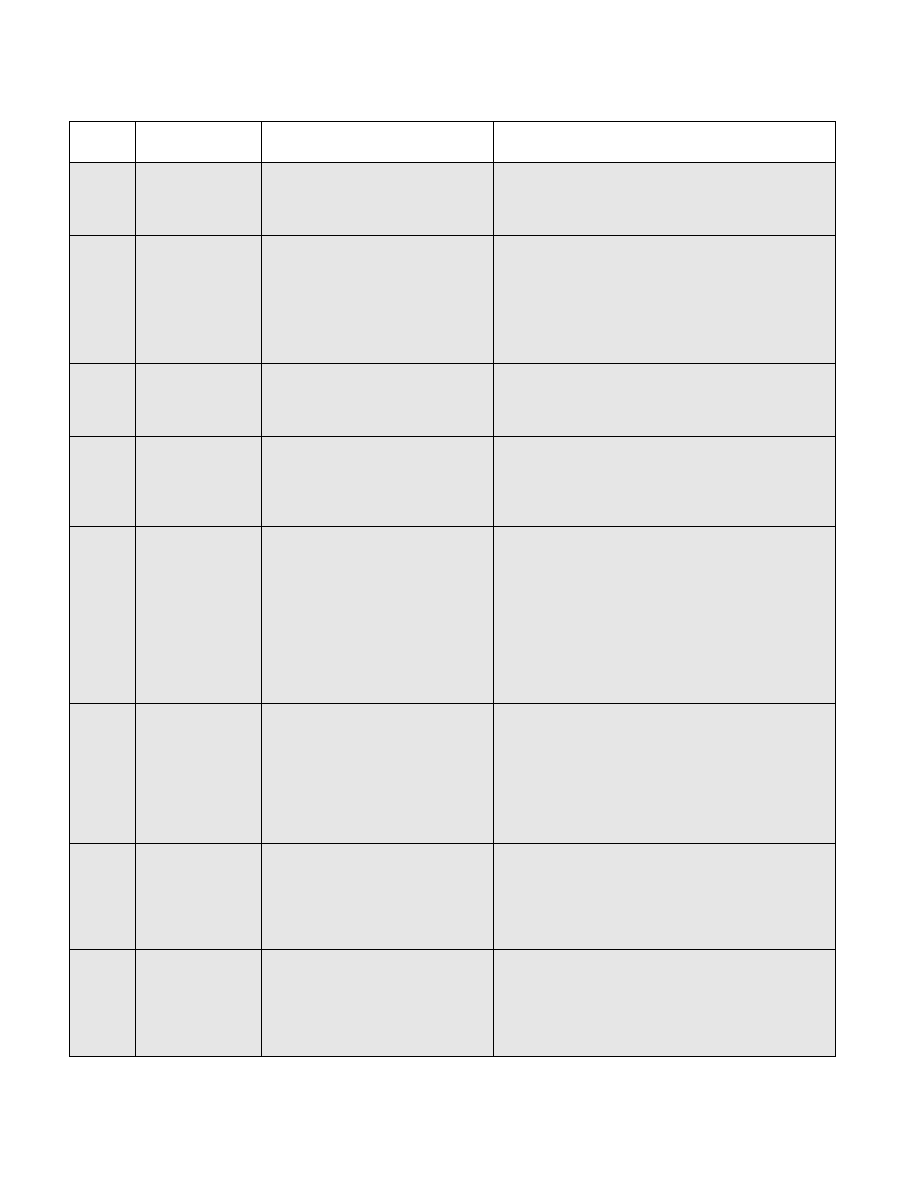

Vol. 3B 19-219

PERFORMANCE-MONITORING EVENTS

33H

D1_STARVATION_

AND_FIFO_IS_

EMPTY

(Counter 0)

Number of times D1 stage cannot

issue ANY instructions since the FIFO

buffer is empty

The D1 stage can issue 0, 1, or 2 instructions per clock if

those are available in an instructions FIFO buffer.

33H

D1_STARVATION_

AND_ONLY_ONE_

INSTRUCTION_IN_

FIFO

(Counter 1)

Number of times the D1 stage issues a

single instruction (since the FIFO

buffer had just one instruction ready)

The D1 stage can issue 0, 1, or 2 instructions per clock if

those are available in an instructions FIFO buffer.

When combined with the previously defined events,

Instruction Executed (16H) and Instruction Executed in

the V-pipe (17H), this event enables the user to calculate

the numbers of time pairing rules prevented issuing of

two instructions.

34H

MMX_

INSTRUCTION_

DATA_WRITES

(Counter 0)

Number of data writes caused by MMX

instructions

34H

MMX_

INSTRUCTION_

DATA_WRITE_

MISSES

(Counter 1)

Number of data write misses caused

by MMX instructions

35H

PIPELINE_

FLUSHES_DUE_

TO_WRONG_

BRANCH_

PREDICTIONS

(Counter 0)

Number of pipeline flushes due to

wrong branch predictions resolved in

either the E-stage or the WB-stage

The count includes any pipeline flush due to a branch that

the pipeline did not follow correctly. It includes cases

where a branch was not in the BTB, cases where a branch

was in the BTB but was mispredicted, and cases where a

branch was correctly predicted but to the wrong address.

Branches are resolved in either the Execute stage

(E-stage) or the Writeback stage (WB-stage). In the later

case, the misprediction penalty is larger by one clock. The

difference between the 35H event count in counter 0 and

counter 1 is the number of E-stage resolved branches.

35H

PIPELINE_

FLUSHES_DUE_

TO_WRONG_

BRANCH_

PREDICTIONS_

RESOLVED_IN_

WB-STAGE

(Counter 1)

Number of pipeline flushes due to

wrong branch predictions resolved in

the WB-stage

See note for event 35H (Counter 0).

36H

MISALIGNED_

DATA_MEMORY_

REFERENCE_ON_

MMX_

INSTRUCTIONS

(Counter 0)

Number of misaligned data memory

references when executing MMX

instructions

36H

PIPELINE_

ISTALL_FOR_MMX_

INSTRUCTION_

DATA_MEMORY_

READS

(Counter 1)

Number clocks during pipeline stalls

caused by waits form MMX instruction

data memory reads

T3:

Table 19-38. Events That Can Be Counted with Pentium Processor Performance-Monitoring Counters (Contd.)

Event

Num.

Mnemonic Event

Name

Description

Comments