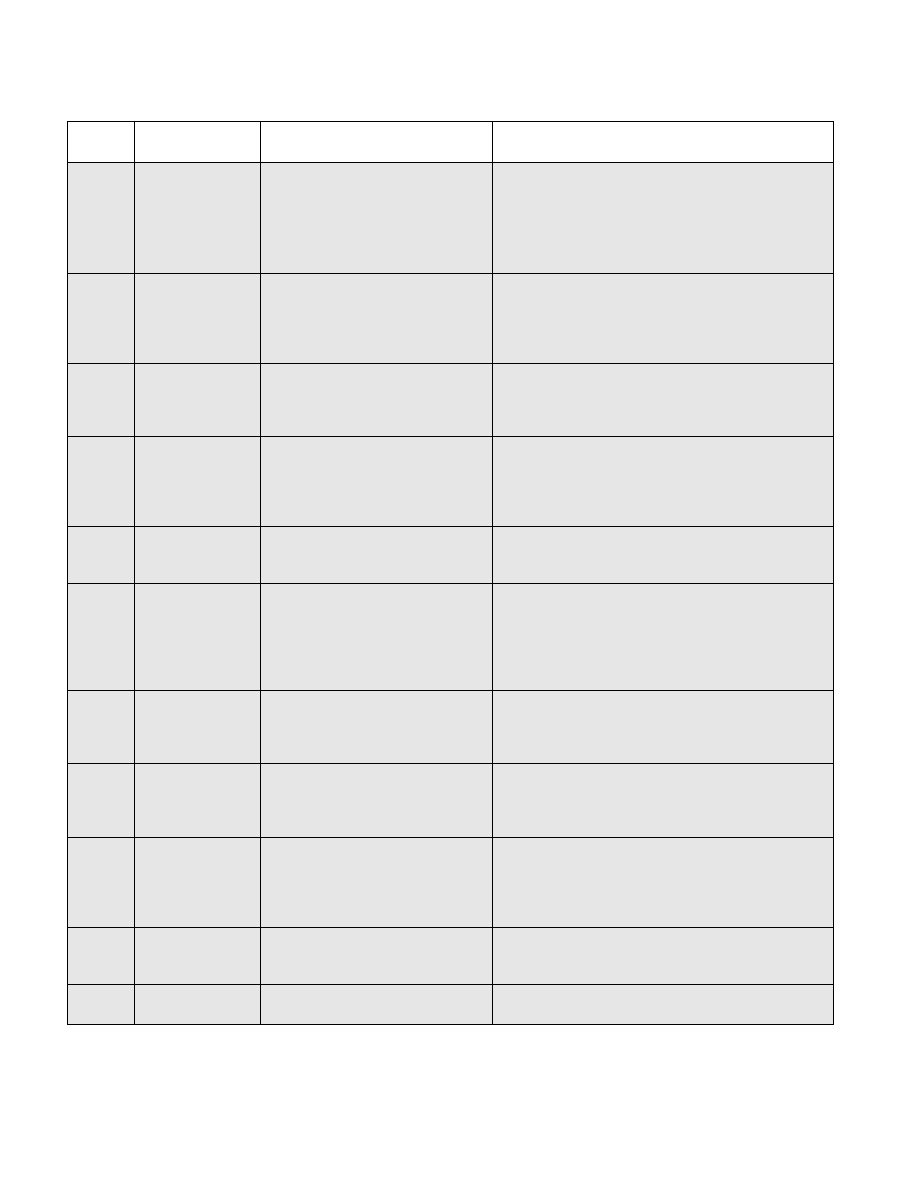

19-218 Vol. 3B

PERFORMANCE-MONITORING EVENTS

2DH

TRANSITIONS_

BETWEEN_MMX_

AND_FP_

INSTRUCTIONS

(Counter 1)

Number of transitions between MMX

and floating-point instructions or vice

versa

An even count indicates the processor

is in MMX state. an odd count indicates

it is in FP state.

This event counts the first floating-point instruction

following an MMX instruction or first MMX instruction

following a floating-point instruction.

The count may be used to estimate the penalty in

transitions between floating-point state and MMX state.

2EH

BUS_UTILIZATION_

DUE_TO_

PROCESSOR_

ACTIVITY

(Counter 0)

Number of clocks the bus is busy due

to the processor’s own activity (the

bus activity that is caused by the

processor)

2EH

WRITES_TO_

NONCACHEABLE_

MEMORY

(Counter 1)

Number of write accesses to

noncacheable memory

The count includes write cycles caused by TLB misses and

I/O write cycles.

Cycles restarted due to BOFF# are not re-counted.

2FH

SATURATING_

MMX_

INSTRUCTIONS_

EXECUTED (Counter

0)

Number of saturating MMX

instructions executed, independently

of whether they actually saturated.

2FH

SATURATIONS_

PERFORMED

(Counter 1)

Number of MMX instructions that used

saturating arithmetic when at least

one of its results actually saturated

If an MMX instruction operating on 4 doublewords

saturated in three out of the four results, the counter will

be incremented by one only.

30H

NUMBER_OF_

CYCLES_NOT_IN_

HALT_STATE

(Counter 0)

Number of cycles the processor is not

idle due to HLT instruction

This event will enable the user to calculate “net CPI”. Note

that during the time that the processor is executing the

HLT instruction, the Time-Stamp Counter is not disabled.

Since this event is controlled by the Counter Controls CC0,

CC1 it can be used to calculate the CPI at CPL=3, which

the TSC cannot provide.

30H

DATA_CACHE_

TLB_MISS_

STALL_DURATION

(Counter 1)

Number of clocks the pipeline is stalled

due to a data cache translation look-

aside buffer (TLB) miss

31H

MMX_

INSTRUCTION_

DATA_READS

(Counter 0)

Number of MMX instruction data reads

31H

MMX_

INSTRUCTION_

DATA_READ_

MISSES

(Counter 1)

Number of MMX instruction data read

misses

32H

FLOATING_POINT_S

TALLS_DURATION

(Counter 0)

Number of clocks while pipe is stalled

due to a floating-point freeze

32H

TAKEN_BRANCHES

(Counter 1)

Number of taken branches

Table 19-38. Events That Can Be Counted with Pentium Processor Performance-Monitoring Counters (Contd.)

Event

Num.

Mnemonic Event

Name

Description

Comments