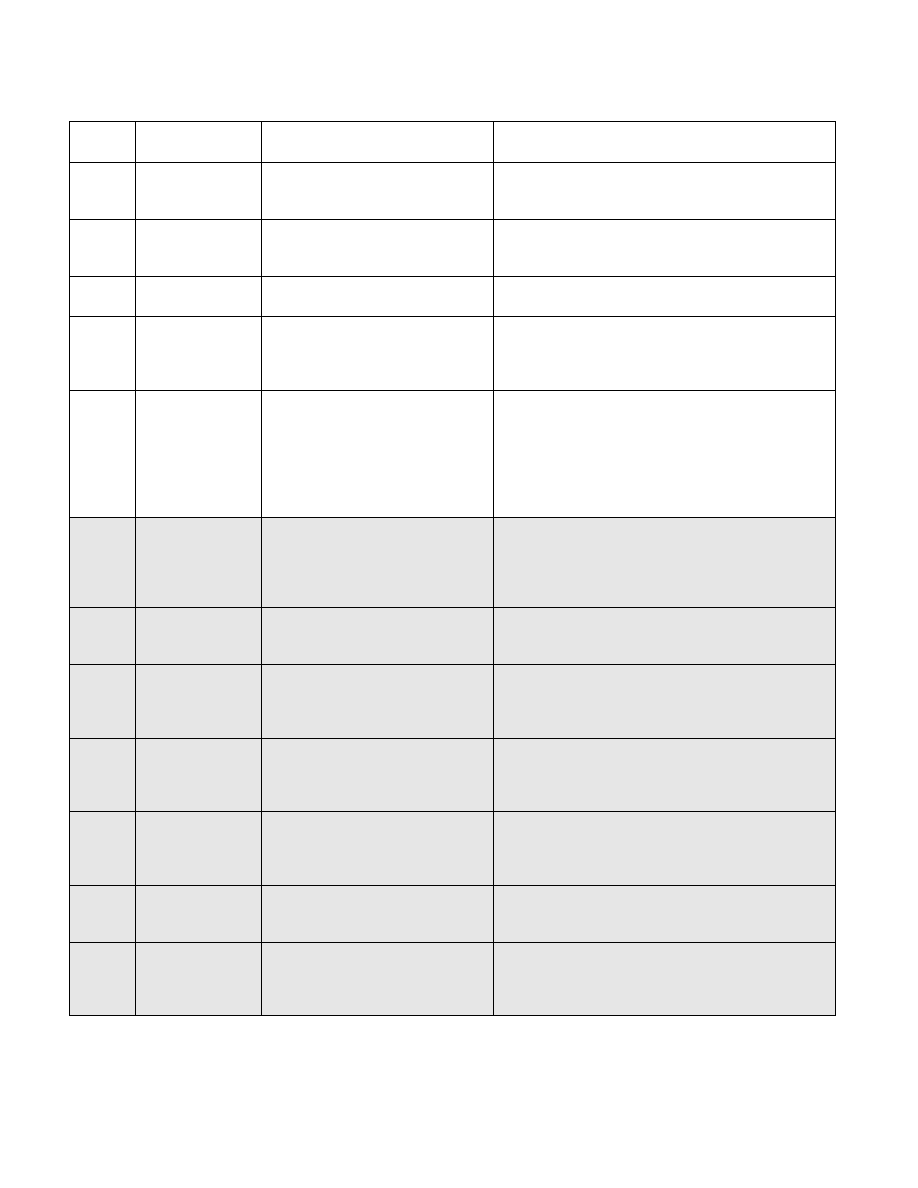

Vol. 3B 19-217

PERFORMANCE-MONITORING EVENTS

25H

BREAKPOINT

MATCH ON DR2

REGISTER

Number of matches on register DR2

breakpoint.

See comment for 23H event.

26H

BREAKPOINT

MATCH ON DR3

REGISTER

Number of matches on register DR3

breakpoint.

See comment for 23H event.

27H

HARDWARE

INTERRUPTS

Number of taken INTR and NMI

interrupts.

28H

DATA_READ_OR_

WRITE

Number of memory data reads and/or

writes (internal data cache hit and

miss combined).

Split cycle reads and writes are counted individually. Data

Memory Reads that are part of TLB miss processing are

not included. These events may occur at a maximum of

two per clock. I/O is not included.

29H

DATA_READ_MISS

OR_WRITE MISS

Number of memory read and/or write

accesses that miss the internal data

cache, whether or not the access is

cacheable or noncacheable.

Additional reads to the same cache line after the first

BRDY# of the burst line fill is returned but before the final

(fourth) BRDY# has been returned, will not cause the

counter to be incremented additional times.

Data accesses that are part of TLB miss processing are

not included. Accesses directed to I/O space are not

included.

2AH

BUS_OWNERSHIP_

LATENCY

(Counter 0)

The time from LRM bus ownership

request to bus ownership granted

(that is, the time from the earlier of a

PBREQ (0), PHITM# or HITM#

assertion to a PBGNT assertion)

The ratio of the 2AH events counted on counter 0 and

counter 1 is the average stall time due to bus ownership

conflict.

2AH

BUS OWNERSHIP

TRANSFERS

(Counter 1)

The number of buss ownership

transfers (that is, the number of

PBREQ (0) assertions

The ratio of the 2AH events counted on counter 0 and

counter 1 is the average stall time due to bus ownership

conflict.

2BH

MMX_

INSTRUCTIONS_

EXECUTED_

U-PIPE (Counter 0)

Number of MMX instructions executed

in the U-pipe

2BH

MMX_

INSTRUCTIONS_

EXECUTED_

V-PIPE (Counter 1)

Number of MMX instructions executed

in the V-pipe

2CH

CACHE_M-

STATE_LINE_

SHARING

(Counter 0)

Number of times a processor identified

a hit to a modified line due to a

memory access in the other processor

(PHITM (O))

If the average memory latencies of the system are known,

this event enables the user to count the Write Backs on

PHITM(O) penalty and the Latency on Hit Modified(I)

penalty.

2CH

CACHE_LINE_

SHARING

(Counter 1)

Number of shared data lines in the L1

cache (PHIT (O))

2DH

EMMS_

INSTRUCTIONS_

EXECUTED (Counter

0)

Number of EMMS instructions

executed

Table 19-38. Events That Can Be Counted with Pentium Processor Performance-Monitoring Counters (Contd.)

Event

Num.

Mnemonic Event

Name

Description

Comments