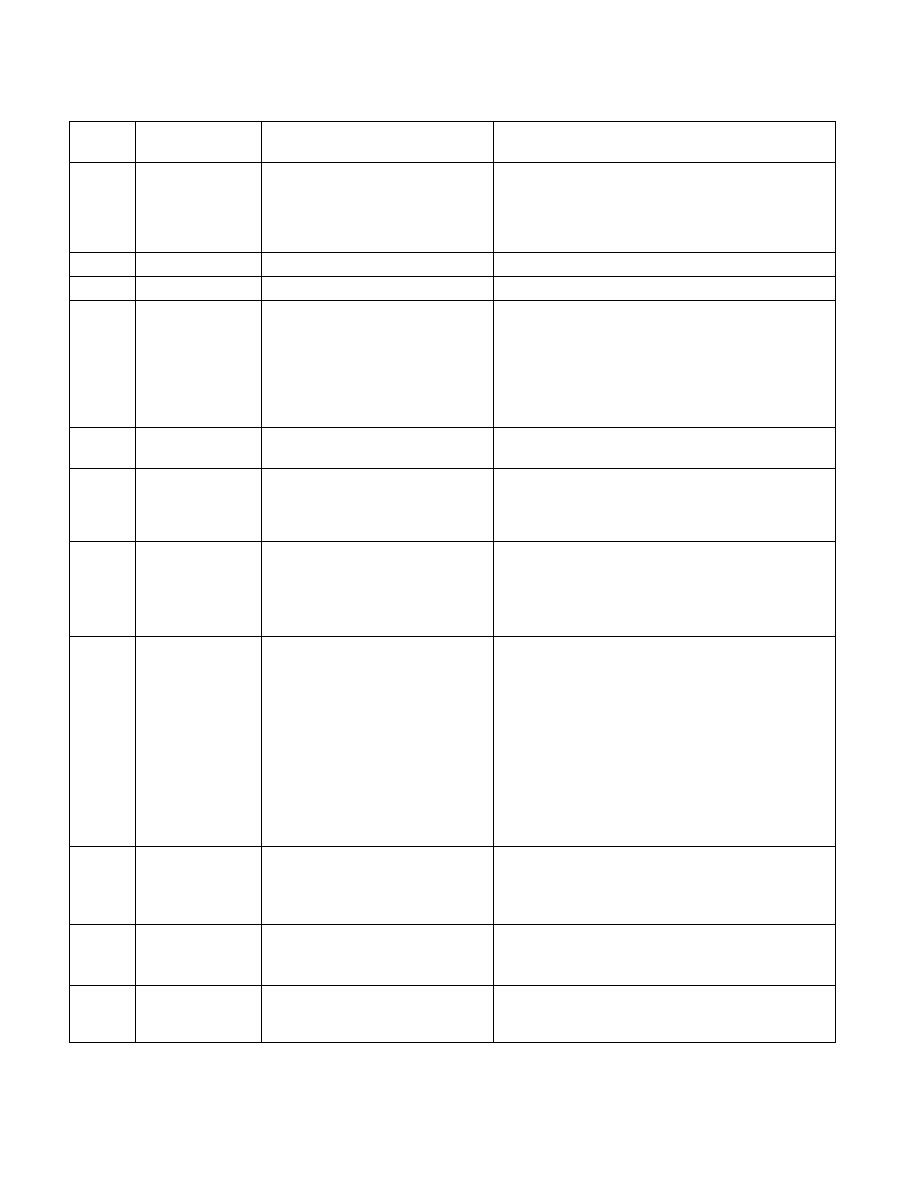

Vol. 3B 19-215

PERFORMANCE-MONITORING EVENTS

0FH

ANY SEGMENT

REGISTER LOADED

Number of writes into any segment

register in real or protected mode

including the LDTR, GDTR, IDTR, and

TR.

Segment loads are caused by explicit segment register

load instructions, far control transfers, and task switches.

Far control transfers and task switches causing a privilege

level change will signal this event twice. Interrupts and

exceptions may initiate a far control transfer.

10H

Reserved

11H

Reserved

12H

Branches

Number of taken and not taken

branches, including: conditional

branches, jumps, calls, returns,

software interrupts, and interrupt

returns.

Also counted as taken branches are serializing

instructions, VERR and VERW instructions, some segment

descriptor loads, hardware interrupts (including FLUSH#),

and programmatic exceptions that invoke a trap or fault

handler. The pipe is not necessarily flushed.

The number of branches actually executed is measured,

not the number of predicted branches.

13H

BTB_HITS

Number of BTB hits that occur.

Hits are counted only for those instructions that are

actually executed.

14H

TAKEN_BRANCH_

OR_BTB_HIT

Number of taken branches or BTB hits

that occur.

This event type is a logical OR of taken branches and BTB

hits. It represents an event that may cause a hit in the

BTB. Specifically, it is either a candidate for a space in the

BTB or it is already in the BTB.

15H

PIPELINE FLUSHES

Number of pipeline flushes that occur

Pipeline flushes are caused by BTB

misses on taken branches,

mispredictions, exceptions, interrupts,

and some segment descriptor loads.

The counter will not be incremented for serializing

instructions (serializing instructions cause the prefetch

queue to be flushed but will not trigger the Pipeline

Flushed event counter) and software interrupts (software

interrupts do not flush the pipeline).

16H

INSTRUCTIONS_

EXECUTED

Number of instructions executed (up

to two per clock).

Invocations of a fault handler are considered instructions.

All hardware and software interrupts and exceptions will

also cause the count to be incremented. Repeat prefixed

string instructions will only increment this counter once

despite the fact that the repeat loop executes the same

instruction multiple times until the loop criteria is

satisfied.

This applies to all the Repeat string instruction prefixes

(i.e., REP, REPE, REPZ, REPNE, and REPNZ). This counter

will also only increment once per each HLT instruction

executed regardless of how many cycles the processor

remains in the HALT state.

17H

INSTRUCTIONS_

EXECUTED_ V PIPE

Number of instructions executed in

the V_pipe.

The event indicates the number of

instructions that were paired.

This event is the same as the 16H event except it only

counts the number of instructions actually executed in

the V-pipe.

18H

BUS_CYCLE_

DURATION

Number of clocks while a bus cycle is in

progress.

This event measures bus use.

The count includes HLDA, AHOLD, and BOFF# clocks.

19H

WRITE_BUFFER_

FULL_STALL_

DURATION

Number of clocks while the pipeline is

stalled due to full write buffers.

Full write buffers stall data memory read misses, data

memory write misses, and data memory write hits to S-

state lines. Stalls on I/O accesses are not included.

Table 19-38. Events That Can Be Counted with Pentium Processor Performance-Monitoring Counters (Contd.)

Event

Num.

Mnemonic Event

Name

Description

Comments