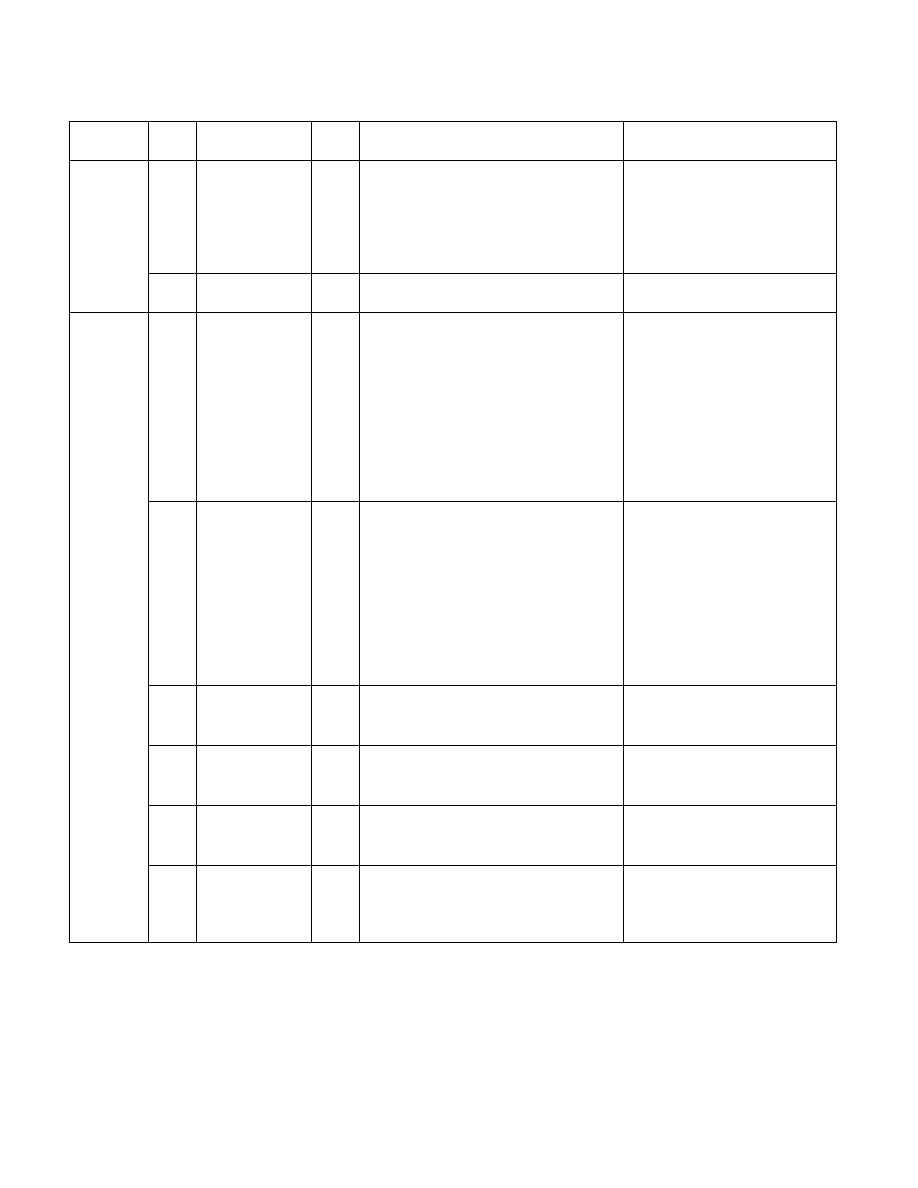

Vol. 3B 19-209

PERFORMANCE-MONITORING EVENTS

• If the PC bit is clear, the

processor toggles the BPMipins

when the counter overflows.

• If the clock ratio is not 2:1 or 3:1,

the BPMi pins will not function

for these performance-

monitoring counter events.

7EH

BUS_SNOOP_

STALL

00H

(Self)

Number of clock cycles during which the bus

is snoop stalled.

Floating-

Point Unit

C1H

FLOPS

00H

Number of computational floating-point

operations retired.

Excludes floating-point computational

operations that cause traps or assists.

Includes floating-point computational

operations executed by the assist handler.

Includes internal sub-operations for complex

floating-point instructions like

transcendentals.

Excludes floating-point loads and stores.

Counter 0 only.

10H

FP_COMP_OPS_

EXE

00H

Number of computational floating-point

operations executed.

The number of FADD, FSUB, FCOM, FMULs,

integer MULs and IMULs, FDIVs, FPREMs,

FSQRTS, integer DIVs, and IDIVs.

This number does not include the number of

cycles, but the number of operations.

This event does not distinguish an FADD

used in the middle of a transcendental flow

from a separate FADD instruction.

Counter 0 only.

11H

FP_ASSIST

00H

Number of floating-point exception cases

handled by microcode.

Counter 1 only.

This event includes counts due to

speculative execution.

12H

MUL

00H

Number of multiplies.

This count includes integer as well as FP

multiplies and is speculative.

Counter 1 only.

13H

DIV

00H

Number of divides.

This count includes integer as well as FP

divides and is speculative.

Counter 1 only.

14H

CYCLES_DIV_

BUSY

00H

Number of cycles during which the divider is

busy, and cannot accept new divides.

This includes integer and FP divides, FPREM,

FPSQRT, etc. and is speculative.

Counter 0 only.

Table 19-37. Events That Can Be Counted with the P6 Family Performance-Monitoring Counters (Contd.)

Unit

Event

Num.

Mnemonic Event

Name

Unit

Mask Description

Comments