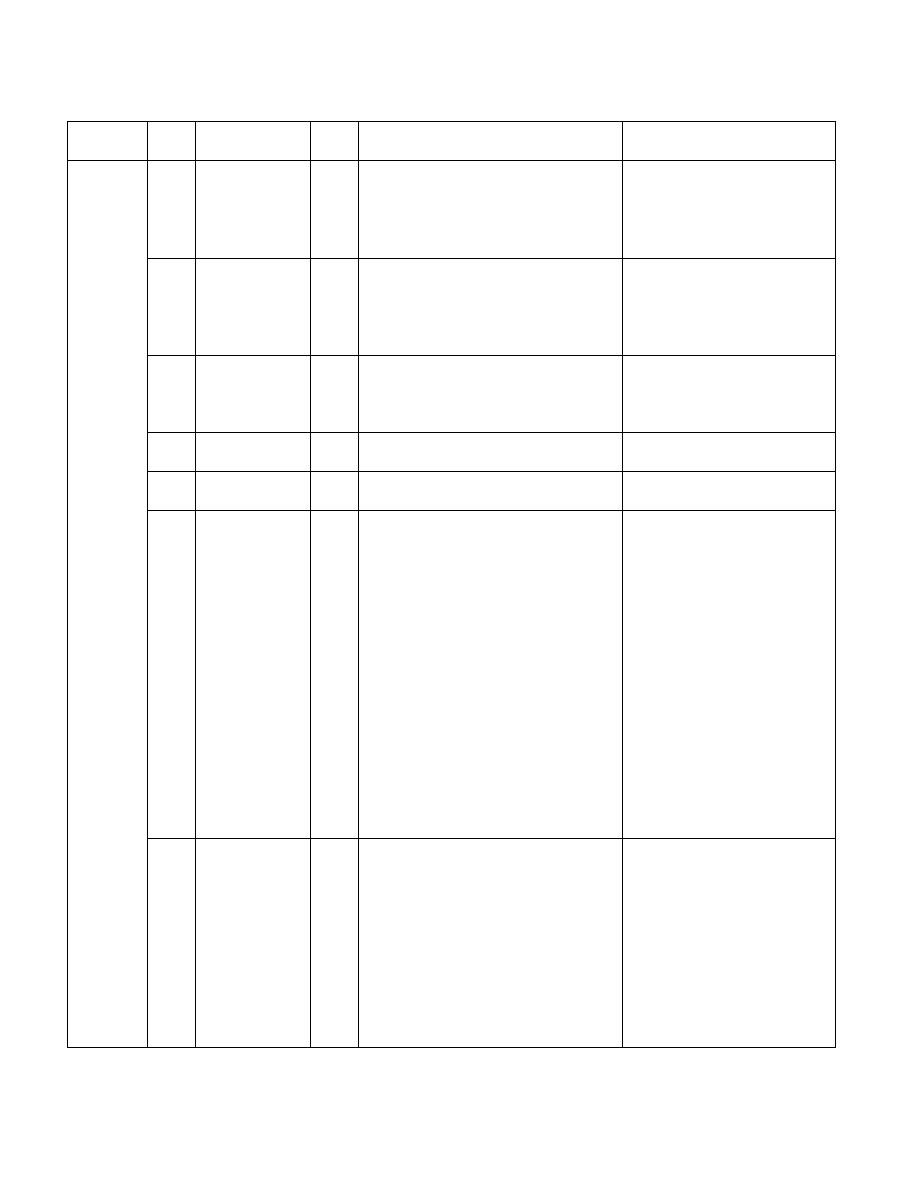

19-208 Vol. 3B

PERFORMANCE-MONITORING EVENTS

6EH

BUS_TRAN_

BURST

00H

(Self)

20H

(Any)

Number of completed burst transactions.

70H

BUS_TRAN_ANY

00H

(Self)

20H

(Any)

Number of all completed bus transactions.

Address bus utilization can be calculated

knowing the minimum address bus

occupancy.

Includes special cycles, etc.

6FH

BUS_TRAN_MEM

00H

(Self)

20H

(Any)

Number of completed memory transactions.

64H

BUS_DATA_RCV

00H

(Self)

Number of bus clock cycles during which this

processor is receiving data.

61H

BUS_BNR_DRV

00H

(Self)

Number of bus clock cycles during which this

processor is driving the BNR# pin.

7AH

BUS_HIT_DRV

00H

(Self)

Number of bus clock cycles during which this

processor is driving the HIT# pin.

Includes cycles due to snoop stalls.

The event counts correctly, but

BPMi (breakpoint monitor) pins

function as follows based on the

setting of the PC bits (bit 19 in the

PerfEvtSel0 and PerfEvtSel1

registers):

• If the core-clock-to- bus-clock

ratio is 2:1 or 3:1, and a PC bit is

set, the BPMi pins will be

asserted for a single clock when

the counters overflow.

• If the PC bit is clear, the

processor toggles the BPMi pins

when the counter overflows.

• If the clock ratio is not 2:1 or 3:1,

the BPMi pins will not function

for these performance-

monitoring counter events.

7BH

BUS_HITM_DRV

00H

(Self)

Number of bus clock cycles during which this

processor is driving the HITM# pin.

Includes cycles due to snoop stalls.

The event counts correctly, but

BPMi (breakpoint monitor) pins

function as follows based on the

setting of the PC bits (bit 19 in the

PerfEvtSel0 and PerfEvtSel1

registers):

• If the core-clock-to- bus-clock

ratio is 2:1 or 3:1, and a PC bit is

set, the BPMi pins will be

asserted for a single clock when

the counters overflow.

Table 19-37. Events That Can Be Counted with the P6 Family Performance-Monitoring Counters (Contd.)

Unit

Event

Num.

Mnemonic Event

Name

Unit

Mask Description

Comments