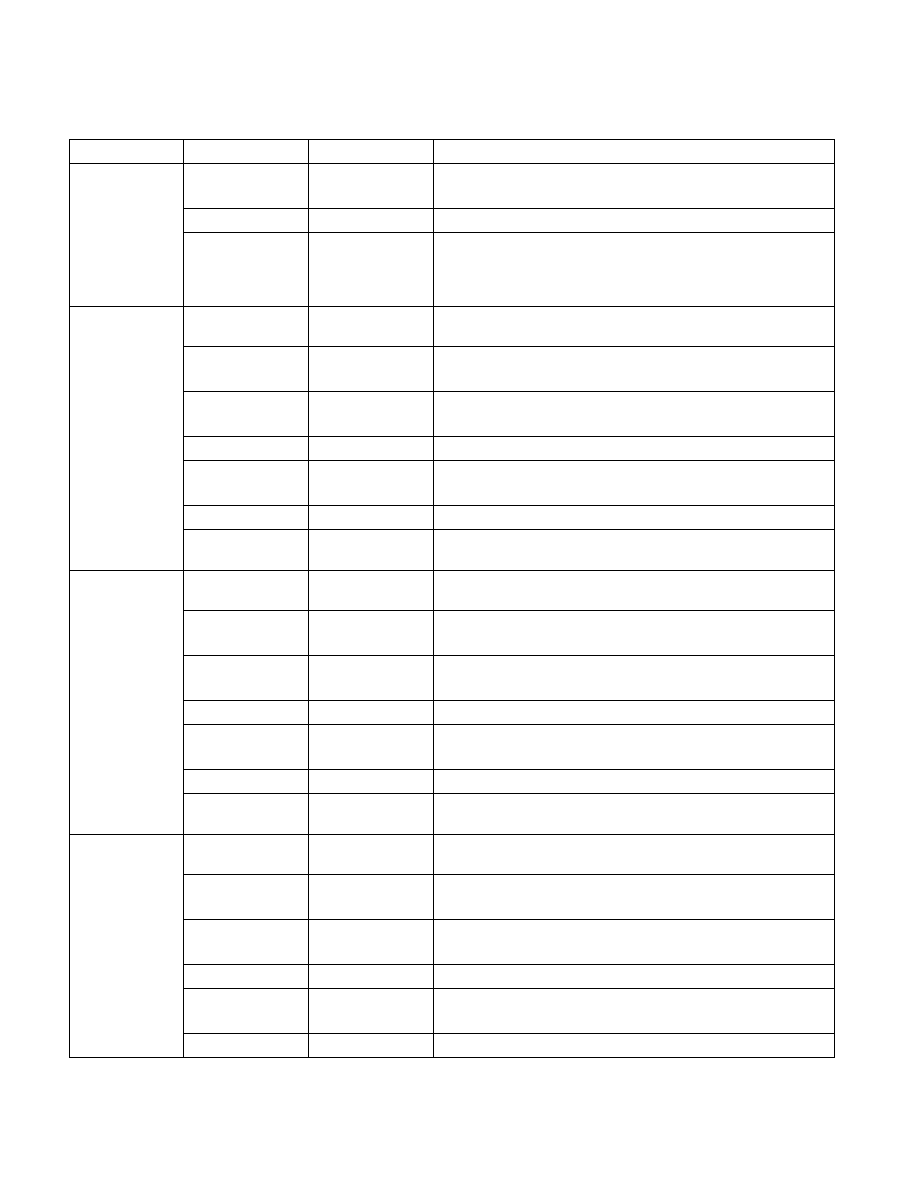

Vol. 3B 19-185

PERFORMANCE-MONITORING EVENTS

ESCR Event Mask

Bit 15: ALL

ESCR[24:9]

Count all μops operating on packed single-precision operands.

CCCR Select

01H

CCCR[15:13]

Event Specific

Notes

1: If an instruction contains more than one packed SP μops, each

packed SP μop that is specified by the event mask will be counted.

2: This metric counts instances of packed memory μops in a repeat

move string.

packed_DP_uop

This event increments for each packed double-precision μop,

specified through the event mask for detection.

ESCR restrictions

MSR_FIRM_ESCR0

MSR_FIRM_ESCR1

Counter numbers

per ESCR

ESCR0: 8, 9

ESCR1: 10, 11

ESCR Event Select

0CH

ESCR[31:25]

ESCR Event Mask

Bit 15: ALL

ESCR[24:9]

Count all μops operating on packed double-precision operands.

CCCR Select

01H

CCCR[15:13]

Event Specific

Notes

If an instruction contains more than one packed DP μops, each

packed DP μop that is specified by the event mask will be counted.

scalar_SP_uop

This event increments for each scalar single-precision μop, specified

through the event mask for detection.

ESCR restrictions

MSR_FIRM_ESCR0

MSR_FIRM_ESCR1

Counter numbers

per ESCR

ESCR0: 8, 9

ESCR1: 10, 11

ESCR Event Select

0AH

ESCR[31:25]

ESCR Event Mask

Bit 15: ALL

ESCR[24:9]

Count all μops operating on scalar single-precision operands.

CCCR Select

01H

CCCR[15:13]

Event Specific

Notes

If an instruction contains more than one scalar SP μops, each scalar

SP μop that is specified by the event mask will be counted.

scalar_DP_uop

This event increments for each scalar double-precision μop, specified

through the event mask for detection.

ESCR restrictions

MSR_FIRM_ESCR0

MSR_FIRM_ESCR1

Counter numbers

per ESCR

ESCR0: 8, 9

ESCR1: 10, 11

ESCR Event Select

0EH

ESCR[31:25]

ESCR Event Mask

Bit 15: ALL

ESCR[24:9]

Count all μops operating on scalar double-precision operands.

CCCR Select

01H

CCCR[15:13]

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description