19-184 Vol. 3B

PERFORMANCE-MONITORING EVENTS

5: Additional overhead may include the time it takes to issue two

requests (the sector by demand and the adjacent sector via

prefetch). Since adjacent sector prefetches have lower priority

that demand fetches, on a heavily used system there is a high

probability that the adjacent sector prefetch will have to wait

until the next bus arbitration.

6: For Pentium 4 and Xeon processors with CPUID model encoding

value less than 3, this event is updated every clock.

7: For Pentium 4 and Xeon processors with CPUID model encoding

value equals to 3 or 4, this event is updated every other clock.

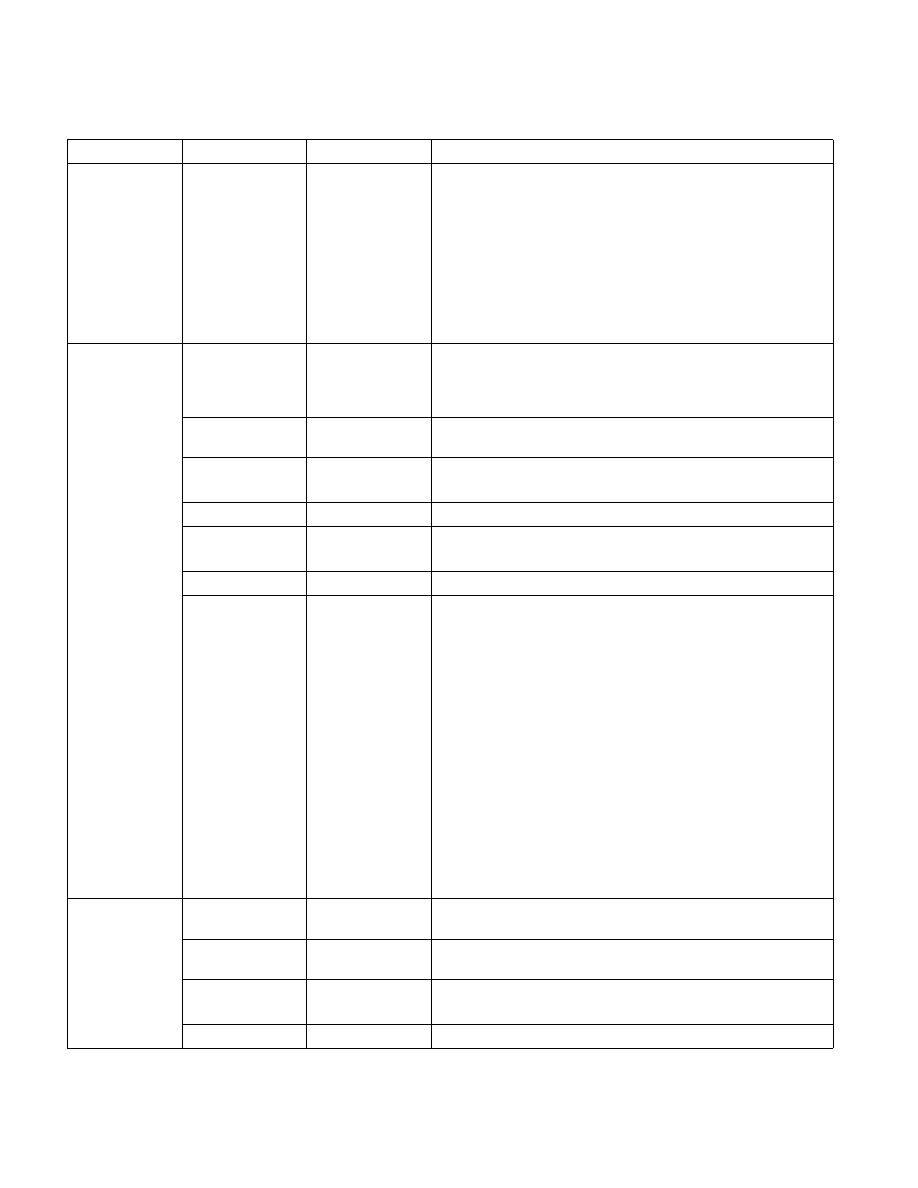

SSE_input_assist

This event counts the number of times an assist is requested to

handle problems with input operands for SSE/SSE2/SSE3 operations;

most notably denormal source operands when the DAZ bit is not set.

Set bit 15 of the event mask to use this event.

ESCR restrictions

MSR_FIRM_ESCR0

MSR_FIRM_ESCR1

Counter numbers

per ESCR

ESCR0: 8, 9

ESCR1: 10, 11

ESCR Event Select

34H

ESCR[31:25]

ESCR Event Mask

15: ALL

ESCR[24:9]

Count assists for SSE/SSE2/SSE3 μops.

CCCR Select

01H

CCCR[15:13]

Event Specific

Notes

1: Not all requests for assists are actually taken. This event is known

to overcount in that it counts requests for assists from

instructions on the non-retired path that do not incur a

performance penalty. An assist is actually taken only for non-

bogus μops. Any appreciable counts for this event are an

indication that the DAZ or FTZ bit should be set and/or the source

code should be changed to eliminate the condition.

2: Two common situations for an SSE/SSE2/SSE3 operation needing

an assist are: (1) when a denormal constant is used as an input and

the Denormals-Are-Zero (DAZ) mode is not set, (2) when the input

operand uses the underflowed result of a previous

SSE/SSE2/SSE3 operation and neither the DAZ nor Flush-To-Zero

(FTZ) modes are set.

3: Enabling the DAZ mode prevents SSE/SSE2/SSE3 operations from

needing assists in the first situation. Enabling the FTZ mode

prevents SSE/SSE2/SSE3 operations from needing assists in the

second situation.

packed_SP_uop

This event increments for each packed single-precision μop,

specified through the event mask for detection.

ESCR restrictions

MSR_FIRM_ESCR0

MSR_FIRM_ESCR1

Counter numbers

per ESCR

ESCR0: 8, 9

ESCR1: 10, 11

ESCR Event Select

08H

ESCR[31:25]

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description