Vol. 3B 19-183

PERFORMANCE-MONITORING EVENTS

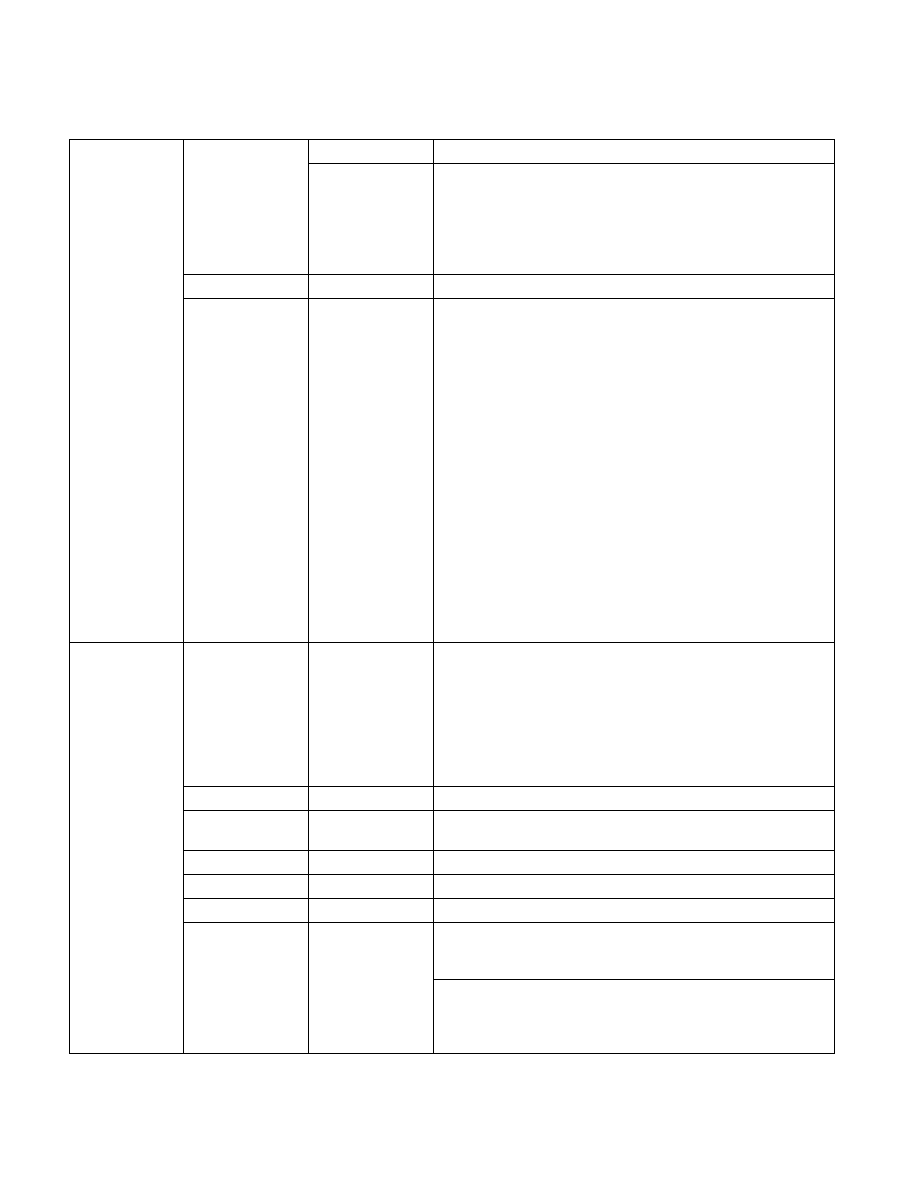

11: MEM_TYPE0

12: MEM_TYPE1

13: MEM_TYPE2

Memory type encodings (bit 11-13) are:

0 – UC

1 – WC

4 – WT

5 – WP

6 – WB

CCCR Select

07H

CCCR[15:13]

Event Specific

Notes

1: Specify edge trigger in CCCR to avoid double counting.

2: A writebacks to 3rd level cache from 2nd level cache counts as a

separate entry, this is in additional to the entry allocated for a

request to the bus.

3: A read request to WB memory type results in a request to the

64-byte sector, containing the target address, followed by a

prefetch request to an adjacent sector.

4: For Pentium 4 and Xeon processors with CPUID model encoding

value equals to 0 and 1, an allocated BSQ entry includes both the

demand sector and prefetched 2nd sector.

5: An allocated BSQ entry for a data chunk is any request less than

64 bytes.

6a:This event may undercount for requests of split type transactions

if the data address straddled across modulo-64 byte boundary.

6b:This event may undercount for requests of read request of

16-byte operands from WC or UC address.

6c:This event may undercount WC partial requests originated from

store operands that are

dwords.

bsq_active_

entries

This event represents the number of BSQ entries (clipped at 15)

currently active (valid) which meet the subevent mask criteria during

allocation in the BSQ. Active request entries are allocated on the BSQ

until de-allocated.

De-allocation of an entry does not necessarily imply the request is

filled. This event must be programmed in conjunction with

BSQ_allocation. Specify one or more event mask bits to select the

transactions that is counted.

ESCR restrictions

ESCR1

Counter numbers

per ESCR

ESCR1: 2, 3

ESCR Event Select

06H

ESCR[30:25]

ESCR Event Mask

ESCR[24:9]

CCCR Select

07H

CCCR[15:13]

Event Specific

Notes

1: Specified desired mask bits in ESCR0 and ESCR1.

2: See the BSQ_allocation event for descriptions of the mask bits.

3: Edge triggering should not be used when counting cycles.

4: This event can be used to estimate the latency of a transaction

from allocation to de-allocation in the BSQ. The latency observed

by BSQ_allocation includes the latency of FSB, plus additional

overhead.

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description