Vol. 3B 19-181

PERFORMANCE-MONITORING EVENTS

5b:For Pentium 4 and Xeon Processors starting with CPUID MODEL

field encoding less than 2, this event is triggered by evaluating

the logical expression [((Request type) or Bit 5 or Bit 6) or

(Memory type)] and (Source agent). Event mask bits for memory

type are ignored if either ALL_READ or ALL_WRITE is specified.

5c:This event is known to ignore CPL in the current implementations

of Pentium 4 and Xeon Processors Both user requests and OS

requests are included in the count.

6: An allocated entry can be a full line (64 bytes) or in individual

chunks of 8 bytes.

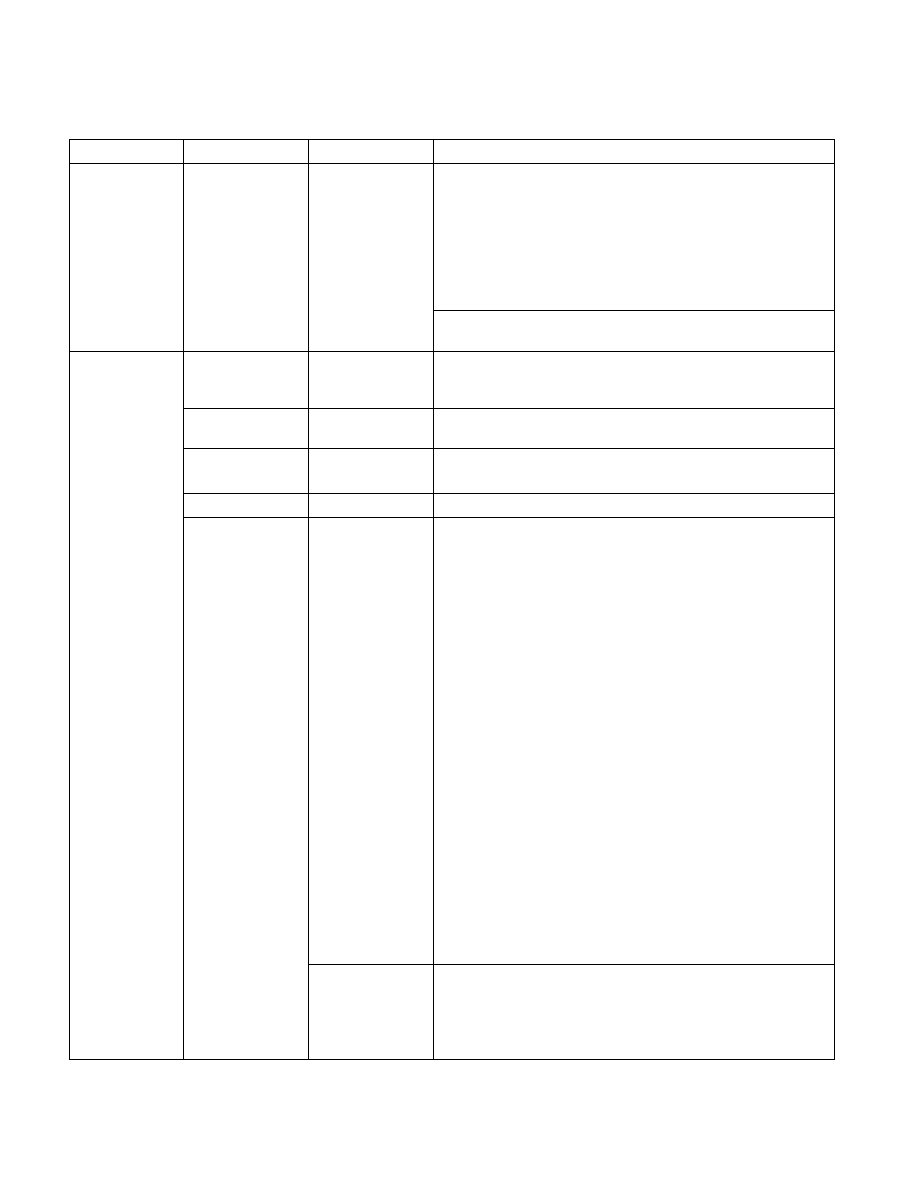

FSB_data_

activity

This event increments once for each DRDY or DBSY event that

occurs on the front side bus. The event allows selection of a specific

DRDY or DBSY event.

ESCR restrictions

MSR_FSB_ESCR0

MSR_FSB_ESCR1

Counter numbers

per ESCR

ESCR0: 0, 1

ESCR1: 2, 3

ESCR Event Select

17H

ESCR[31:25]

ESCR Event Mask

Bit 0:

ESCR[24:9]

DRDY_DRV

Count when this processor drives data onto the bus - includes writes

and implicit writebacks.

Asserted two processor clock cycles for partial writes and 4

processor clocks (usually in consecutive bus clocks) for full line

writes.

1: DRDY_OWN

Count when this processor reads data from the bus - includes loads

and some PIC transactions. Asserted two processor clock cycles for

partial reads and 4 processor clocks (usually in consecutive bus

clocks) for full line reads.

Count DRDY events that we drive.

Count DRDY events sampled that we own.

2: DRDY_OTHER

Count when data is on the bus but not being sampled by the

processor. It may or may not be being driven by this processor.

Asserted two processor clock cycles for partial transactions and 4

processor clocks (usually in consecutive bus clocks) for full line

transactions.

3: DBSY_DRV

Count when this processor reserves the bus for use in the next bus

cycle in order to drive data. Asserted for two processor clock cycles

for full line writes and not at all for partial line writes.

May be asserted multiple times (in consecutive bus clocks) if we stall

the bus waiting for a cache lock to complete.

4: DBSY_OWN

Count when some agent reserves the bus for use in the next bus

cycle to drive data that this processor will sample.

Asserted for two processor clock cycles for full line writes and not at

all for partial line writes. May be asserted multiple times (all one bus

clock apart) if we stall the bus for some reason.

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description