19-180 Vol. 3B

PERFORMANCE-MONITORING EVENTS

6: For write-through (WT) and write-protected (WP) memory types,

this event counts reads as the number of 64-byte sectors. Writes

are counted by individual chunks.

7: For uncacheable (UC) memory types, this event counts the

number of 8-byte chunks allocated.

8: For Pentium 4 and Xeon Processors with CPUID Signature less

than F27H, only MSR_FSB_ESCR0 is available.

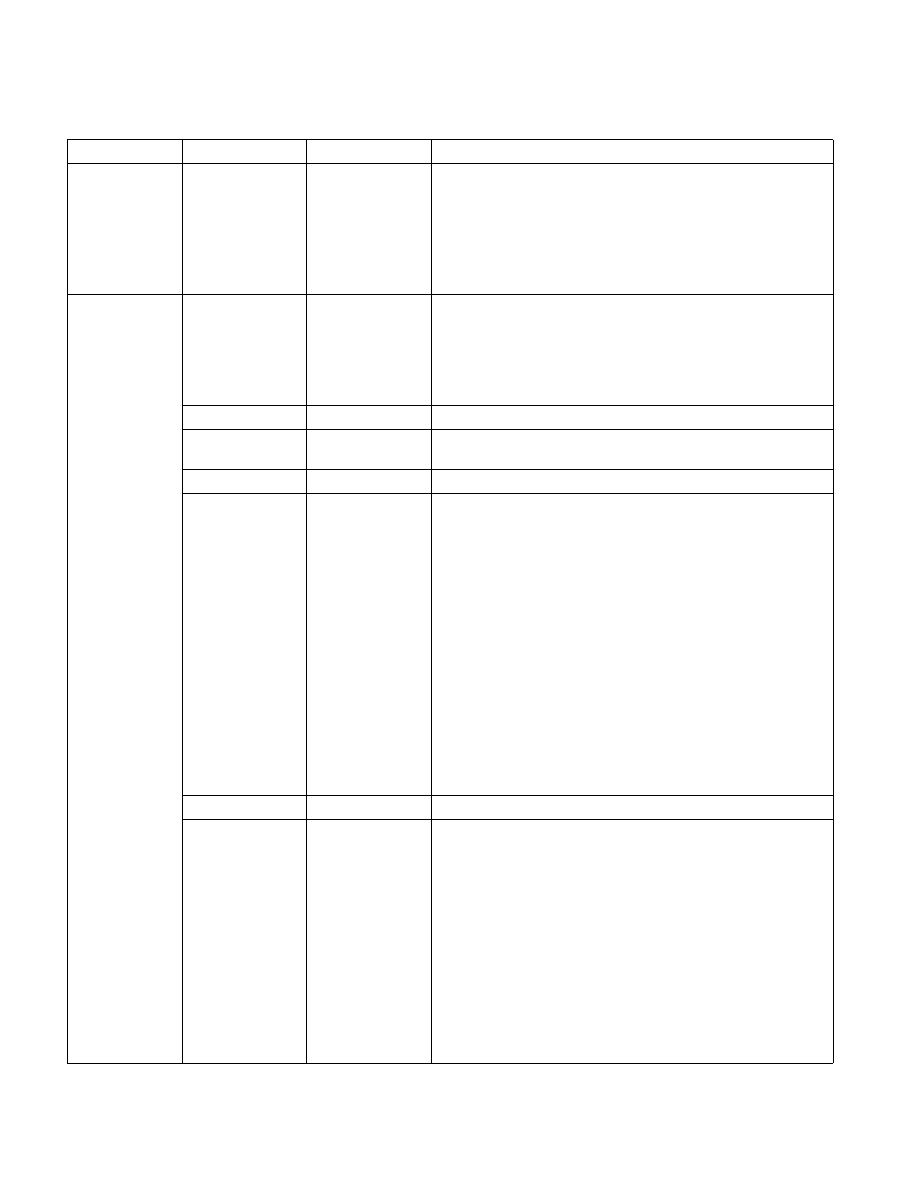

IOQ_active_

entries

This event counts the number of entries (clipped at 15) in the IOQ

that are active. An allocated entry can be a sector (64 bytes) or a

chunks of 8 bytes.

The event must be programmed in conjunction with IOQ_allocation.

Specify one or more event mask bits to select the transactions that

is counted.

ESCR restrictions

MSR_FSB_ESCR1

Counter numbers

per ESCR

ESCR1: 2, 3

ESCR Event Select

01AH

ESCR[30:25]

ESCR Event Mask

Bits

0-4 (single field)

5: ALL_READ

6: ALL_WRITE

7: MEM_UC

8: MEM_WC

ESCR[24:9]

Bus request type (use 00001 for invalid or default).

Count read entries.

Count write entries.

Count UC memory access entries.

Count WC memory access entries.

9: MEM_WT

10: MEM_WP

Count write-through (WT) memory access entries.

Count write-protected (WP) memory access entries.

11: MEM_WB

13: OWN

Count WB memory access entries.

Count all store requests driven by processor, as opposed to other

processor or DMA.

14: OTHER

15: PREFETCH

Count all requests driven by other processors or DMA.

Include HW and SW prefetch requests in the count.

CCCR Select

06H

CCCR[15:13]

Event Specific

Notes

1: Specified desired mask bits in ESCR0 and ESCR1.

2: See the ioq_allocation event for descriptions of the mask bits.

3: Edge triggering should not be used when counting cycles.

4: The mapping of interpreted bit field values to transaction types

may differ across different processor model implementations of

the Pentium 4 processor family. Applications that programs

performance monitoring events should use the CPUID instruction

to detect processor models when using this event. The logical

expression that triggers this event as describe below:

5a:For Pentium 4 and Xeon Processors starting with CPUID MODEL

field encoding equal to 2 or greater, this event is triggered by

evaluating the logical expression ((Request type) and (Bit 5 or Bit

6) and (Memory type) and (Source agent)).

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description