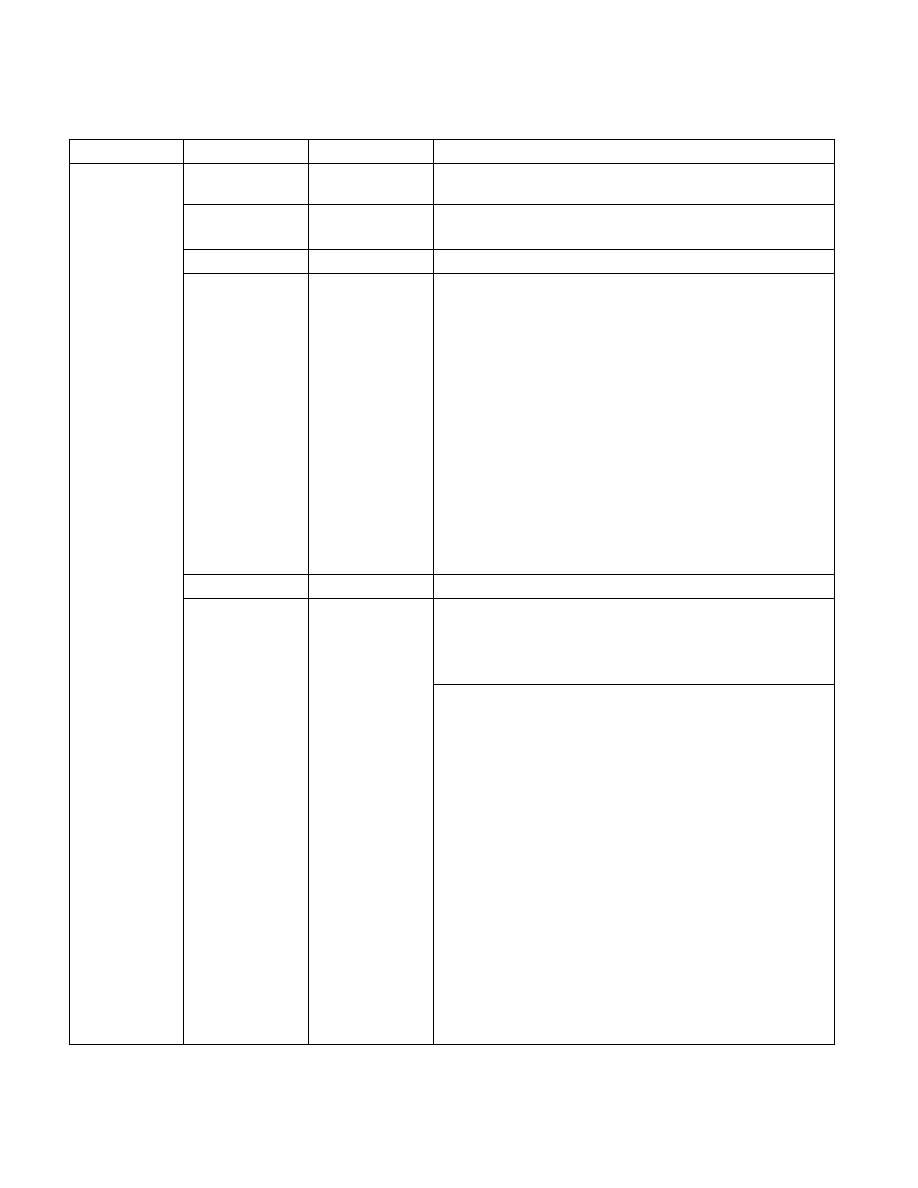

Vol. 3B 19-179

PERFORMANCE-MONITORING EVENTS

ESCR restrictions

MSR_FSB_ESCR0,

MSR_FSB_ESCR1

Counter numbers

per ESCR

ESCR0: 0, 1;

ESCR1: 2, 3

ESCR Event Select

03H

ESCR[31:25]

ESCR Event Mask

Bits

0-4 (single field)

5: ALL_READ

6: ALL_WRITE

7: MEM_UC

8: MEM_WC

ESCR[24:9]

Bus request type (use 00001 for invalid or default).

Count read entries.

Count write entries.

Count UC memory access entries.

Count WC memory access entries.

9: MEM_WT

10: MEM_WP

Count write-through (WT) memory access entries.

Count write-protected (WP) memory access entries.

11: MEM_WB

13: OWN

Count WB memory access entries.

Count all store requests driven by processor, as opposed to other

processor or DMA.

14: OTHER

15: PREFETCH

Count all requests driven by other processors or DMA.

Include HW and SW prefetch requests in the count.

CCCR Select

06H

CCCR[15:13]

Event Specific

Notes

1: If PREFETCH bit is cleared, sectors fetched using prefetch are

excluded in the counts. If PREFETCH bit is set, all sectors or chunks

read are counted.

2: Specify the edge trigger in CCCR to avoid double counting.

3: The mapping of interpreted bit field values to transaction types

may differ with different processor model implementations of the

Pentium 4 processor family. Applications that program

performance monitoring events should use CPUID to determine

processor models when using this event. The logic equations that

trigger the event are model-specific (see 4a and 4b below).

4a:For Pentium 4 and Xeon Processors starting with CPUID Model

field encoding equal to 2 or greater, this event is triggered by

evaluating the logical expression ((Request type) and (Bit 5 or Bit

6) and (Memory type) and (Source agent)).

4b:For Pentium 4 and Xeon Processors with CPUID Model field

encoding less than 2, this event is triggered by evaluating the

logical expression [((Request type) or Bit 5 or Bit 6) or (Memory

type)] and (Source agent). Note that event mask bits for memory

type are ignored if either ALL_READ or ALL_WRITE is specified.

5: This event is known to ignore CPL in early implementations of

Pentium 4 and Xeon Processors. Both user requests and OS

requests are included in the count. This behavior is fixed starting

with Pentium 4 and Xeon Processors with CPUID signature F27H

(Family 15, Model 2, Stepping 7).

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description