19-178 Vol. 3B

PERFORMANCE-MONITORING EVENTS

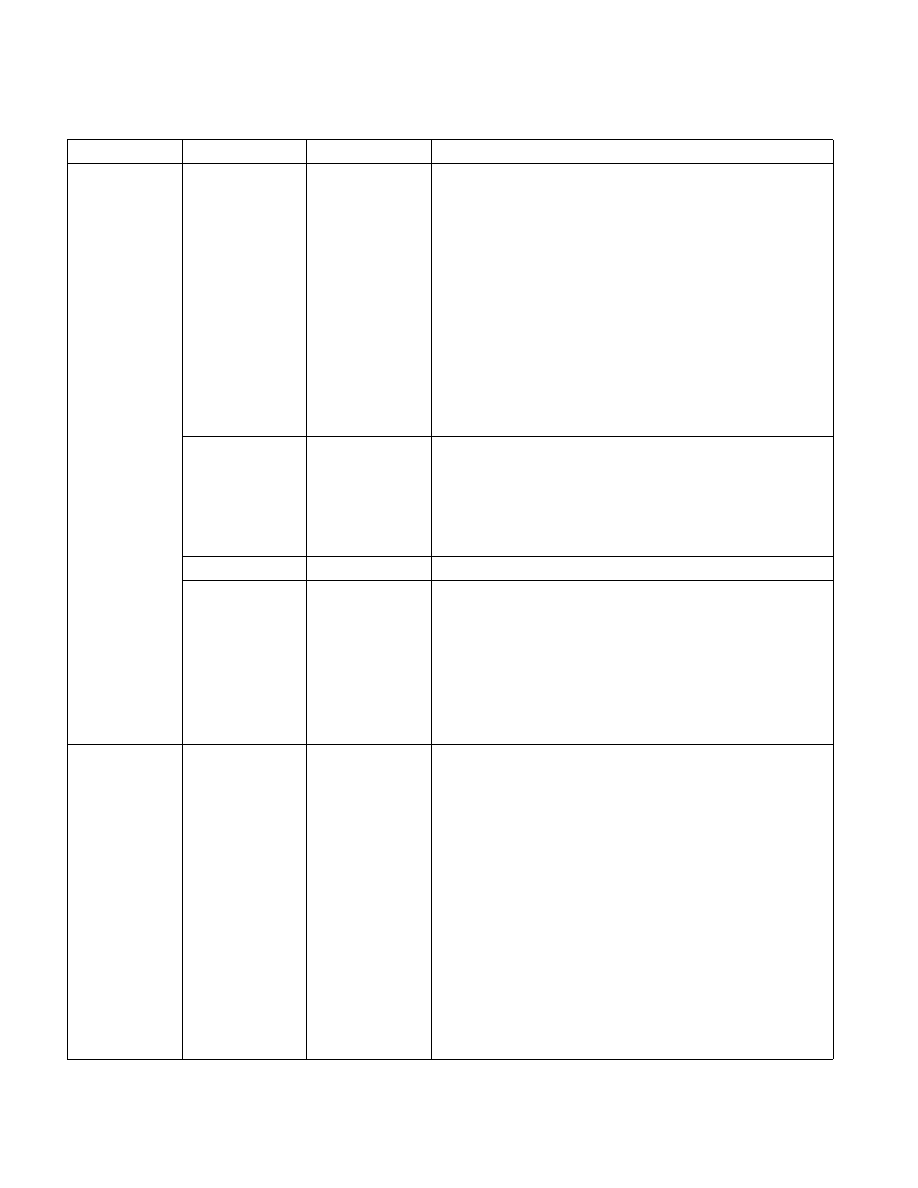

Bit

0: RD_2ndL_HITS

1: RD_2ndL_HITE

2: RD_2ndL_HITM

3: RD_3rdL_HITS

ESCR[24:9]

Read 2nd level cache hit Shared (includes load and RFO).

Read 2nd level cache hit Exclusive (includes load and RFO).

Read 2nd level cache hit Modified (includes load and RFO).

Read 3rd level cache hit Shared (includes load and RFO).

4: RD_3rdL_HITE

5: RD_3rdL_HITM

Read 3rd level cache hit Exclusive (includes load and RFO).

Read 3rd level cache hit Modified (includes load and RFO).

ESCR Event Mask

8: RD_2ndL_MISS

9: RD_3rdL_MISS

10: WR_2ndL_MISS

Read 2nd level cache miss (includes load and RFO).

Read 3rd level cache miss (includes load and RFO).

A Writeback lookup from DAC misses the 2nd level cache (unlikely to

happen).

CCCR Select

07H

CCCR[15:13]

Event Specific

Notes

1: The implementation of this event in current Pentium 4 and Xeon

processors treats either a load operation or a request for

ownership (RFO) request as a “read” type operation.

2: Currently this event causes both over and undercounting by as

much as a factor of two due to an erratum.

3: It is possible for a transaction that is started as a prefetch to

change the transaction's internal status, making it no longer a

prefetch. or change the access result status (hit, miss) as seen by

this event.

IOQ_allocation This

event counts the various types of transactions on the bus. A

count is generated each time a transaction is allocated into the IOQ

that matches the specified mask bits. An allocated entry can be a

sector (64 bytes) or a chunks of 8 bytes.

Requests are counted once per retry. The event mask bits constitute

4 bit fields. A transaction type is specified by interpreting the values

of each bit field.

Specify one or more event mask bits in a bit field to select the value

of the bit field.

Each field (bits 0-4 are one field) are independent of and can be

ORed with the others. The request type field is further combined

with bit 5 and 6 to form a binary expression. Bits 7 and 8 form a bit

field to specify the memory type of the target address.

Bits 13 and 14 form a bit field to specify the source agent of the

request. Bit 15 affects read operation only. The event is triggered by

evaluating the logical expression: (((Request type) OR Bit 5 OR Bit 6)

OR (Memory type)) AND (Source agent).

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description