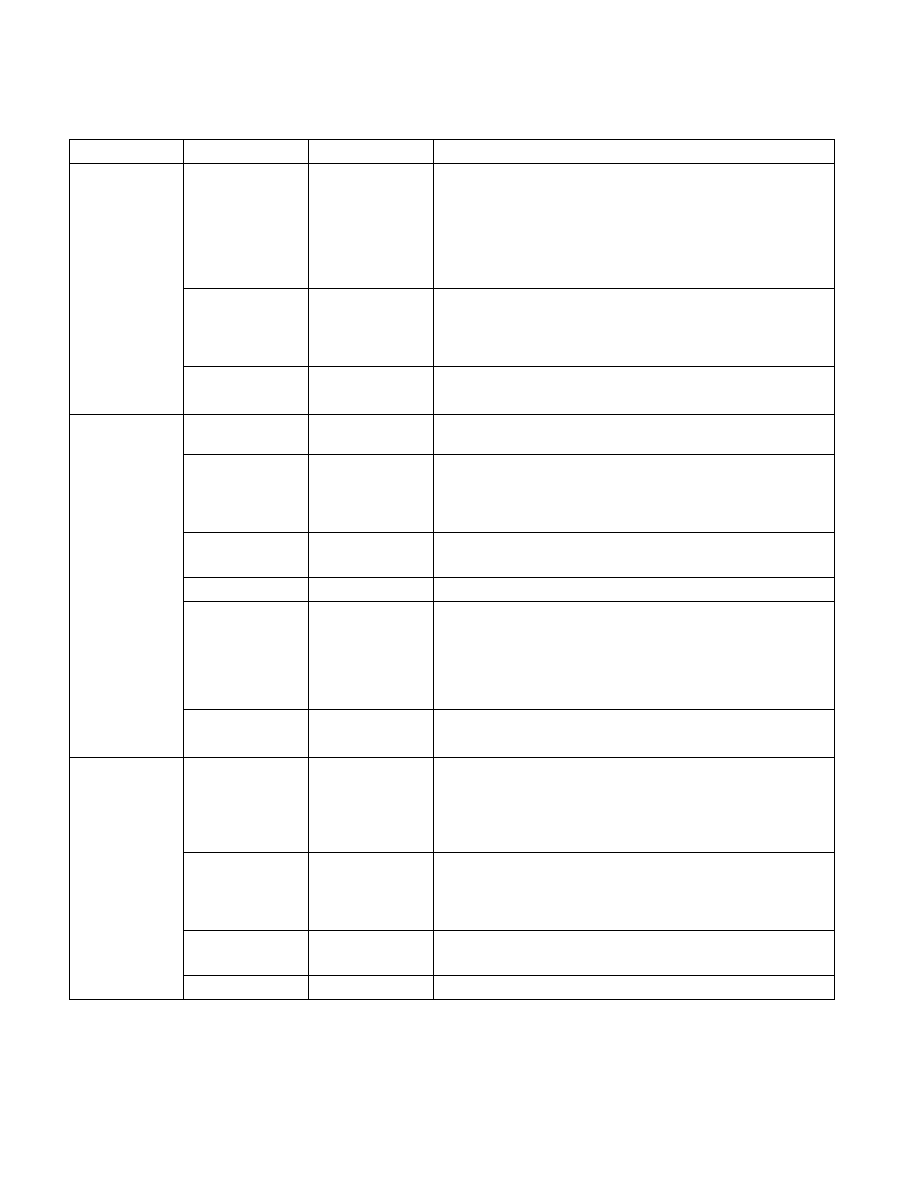

Vol. 3B 19-177

PERFORMANCE-MONITORING EVENTS

ESCR Event Mask

Bit

1: NO_STA

3: NO_STD

ESCR[24:9]

Replayed because of unknown store address.

Replayed because of unknown store data.

4: PARTIAL_DATA

5: UNALGN_ADDR

Replayed because of partially overlapped data access between the

load and store operations.

Replayed because the lower 4 bits of the linear address do not

match between the load and store operations.

CCCR Select

02H

CCCR[15:13]

page_walk_type

This event counts various types of page walks that the page miss

handler (PMH) performs.

ESCR restrictions

MSR_PMH_

ESCR0

MSR_PMH_

ESCR1

Counter numbers

per ESCR

ESCR0: 0, 1

ESCR1: 2, 3

ESCR Event Select

01H

ESCR[31:25]

ESCR Event Mask

Bit

0: DTMISS

1: ITMISS

ESCR[24:9]

Page walk for a data TLB miss (either load or store).

Page walk for an instruction TLB miss.

CCCR Select

04H

CCCR[15:13]

BSQ_cache

_reference

This event counts cache references (2nd level cache or 3rd level

cache) as seen by the bus unit.

Specify one or more mask bit to select an access according to the

access type (read type includes both load and RFO, write type

includes writebacks and evictions) and the access result (hit, misses).

ESCR restrictions

MSR_BSU_

ESCR0

MSR_BSU_

ESCR1

Counter numbers

per ESCR

ESCR0: 0, 1

ESCR1: 2, 3

ESCR Event Select

0CH

ESCR[31:25]

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting (Contd.)

Event Name

Event Parameters Parameter Value

Description