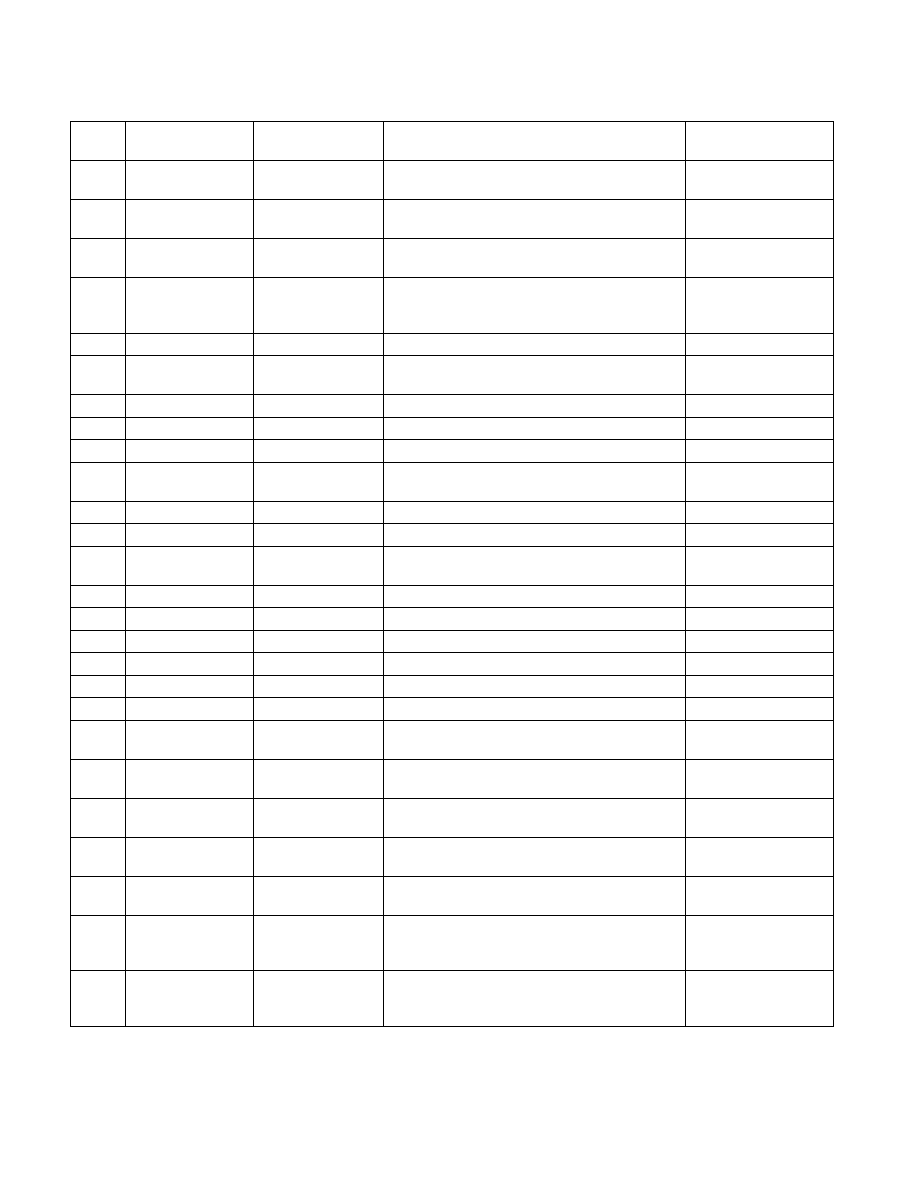

19-172 Vol. 3B

PERFORMANCE-MONITORING EVENTS

B3H

SIMD_Int_Plog_

Exec

10H

Number of SIMD Integer packed logical instructions

executed.

B3H

SIMD_Int_Pari_Exec 20H

Number of SIMD Integer packed arithmetic

instructions executed.

C0H

Instr_Ret

00H

Number of instruction retired (Macro fused

instruction count as 2).

C1H

FP_Comp_Instr_Ret 00H

Number of FP compute instructions retired (X87

instruction or instruction that contains X87

operations).

Use IA32_PMC0 only.

C2H

Uops_Ret

00H

Number of micro-ops retired (include fused uops).

C3H

SMC_Detected

00H

Number of times self-modifying code condition

detected.

C4H

Br_Instr_Ret

00H

Number of branch instructions retired.

C5H

Br_MisPred_Ret

00H

Number of mispredicted branch instructions retired.

C6H

Cycles_Int_Masked

00H

Cycles while interrupt is disabled.

C7H

Cycles_Int_Pedning_

Masked

00H

Cycles while interrupt is disabled and interrupts are

pending.

C8H

HW_Int_Rx

00H

Number of hardware interrupts received.

C9H

Br_Taken_Ret

00H

Number of taken branch instruction retired.

CAH

Br_MisPred_Taken_

Ret

00H

Number of taken and mispredicted branch

instructions retired.

CCH

MMX_FP_Trans

00H

Number of transitions from MMX to X87.

CCH

FP_MMX_Trans

01H

Number of transitions from X87 to MMX.

CDH

MMX_Assist

00H

Number of EMMS executed.

CEH

MMX_Instr_Ret

00H

Number of MMX instruction retired.

D0H

Instr_Decoded

00H

Number of instruction decoded.

D7H

ESP_Uops

00H

Number of ESP folding instruction decoded.

D8H

SIMD_FP_SP_Ret

00H

Number of SSE/SSE2 single precision instructions

retired (packed and scalar).

D8H

SIMD_FP_SP_S_

Ret

01H

Number of SSE/SSE2 scalar single precision

instructions retired.

D8H

SIMD_FP_DP_P_

Ret

02H

Number of SSE/SSE2 packed double precision

instructions retired.

D8H

SIMD_FP_DP_S_

Ret

03H

Number of SSE/SSE2 scalar double precision

instructions retired.

D8H

SIMD_Int_128_Ret

04H

Number of SSE2 128 bit integer instructions

retired.

D9H

SIMD_FP_SP_P_

Comp_Ret

00H

Number of SSE/SSE2 packed single precision

compute instructions retired (does not include AND,

OR, XOR).

D9H

SIMD_FP_SP_S_

Comp_Ret

01H

Number of SSE/SSE2 scalar single precision

compute instructions retired (does not include AND,

OR, XOR).

Table 19-27. Non-Architectural Performance Events in Intel® Core™ Solo and Intel® Core™ Duo Processors (Contd.)

Event

Num.

Event Mask

Mnemonic

Umask

Value

Description

Comment