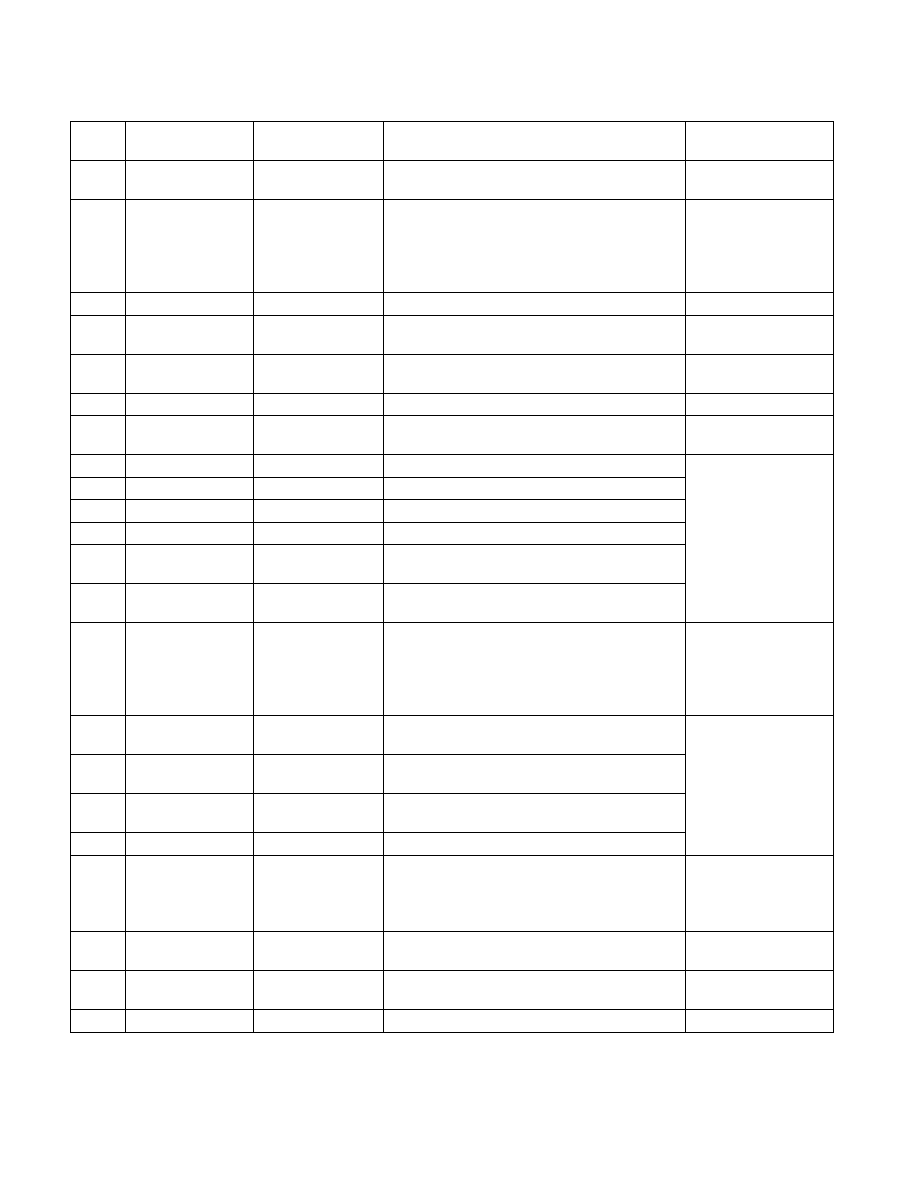

19-170 Vol. 3B

PERFORMANCE-MONITORING EVENTS

4FH

L1_Pref_Req

00H

L1 prefetch requests due to DCU cache misses.

May overcount if

request re-submitted.

60H

Bus_Req_

Outstanding

00; Requires core-

specificity, and agent

specificity

Weighted cycles of cacheable bus data read

requests. This event counts full-line read request

from DCU or HW prefetcher, but not RFO, write,

instruction fetches, or others.

Use Cmask =1 to count

duration.

Use Umask bit 12 to

include HWP or exclude

HWP separately.

61H

Bus_BNR_Clocks

00H

External bus cycles while BNR asserted.

62H

Bus_DRDY_Clocks

00H

External bus cycles while DRDY asserted.

Requires agent

specificity.

63H

Bus_Locks_Clocks

00H

External bus cycles while bus lock signal asserted.

Requires core

specificity.

64H

Bus_Data_Rcv

40H

Number of data chunks received by this processor.

65H

Bus_Trans_Brd

See comment.

Burst read bus transactions (data or code).

Requires core

specificity.

66H

Bus_Trans_RFO

See comment.

Completed read for ownership (RFO) transactions.

Requires agent

specificity.

Requires core

specificity.

Each transaction counts

its address strobe.

Retried transaction may

be counted more than

once.

68H

Bus_Trans_Ifetch

See comment.

Completed instruction fetch transactions.

69H

Bus_Trans_Inval

See comment.

Completed invalidate transactions.

6AH

Bus_Trans_Pwr

See comment.

Completed partial write transactions.

6BH

Bus_Trans_P

See comment.

Completed partial transactions (include partial read

+ partial write + line write).

6CH

Bus_Trans_IO

See comment.

Completed I/O transactions (read and write).

6DH

Bus_Trans_Def

20H

Completed defer transactions.

Requires core

specificity.

Retried transaction may

be counted more than

once.

67H

Bus_Trans_WB

C0H

Completed writeback transactions from DCU (does

not include L2 writebacks).

Requires agent

specificity.

Each transaction counts

its address strobe.

Retried transaction may

be counted more than

once.

6EH

Bus_Trans_Burst

C0H

Completed burst transactions (full line transactions

include reads, write, RFO, and writebacks).

6FH

Bus_Trans_Mem

C0H

Completed memory transactions. This includes

Bus_Trans_Burst + Bus_Trans_P+Bus_Trans_Inval.

70H

Bus_Trans_Any

C0H

Any completed bus transactions.

77H

Bus_Snoops

00H

Counts any snoop on the bus.

Requires MESI

qualification.

Requires agent

specificity.

78H

DCU_Snoop_To_

Share

01H

DCU snoops to share-state L1 cache line due to L1

misses.

Requires core

specificity.

7DH

Bus_Not_In_Use

00H

Number of cycles there is no transaction from the

core.

Requires core

specificity.

7EH

Bus_Snoop_Stall

00H

Number of bus cycles while bus snoop is stalled.

Table 19-27. Non-Architectural Performance Events in Intel® Core™ Solo and Intel® Core™ Duo Processors (Contd.)

Event

Num.

Event Mask

Mnemonic

Umask

Value

Description

Comment