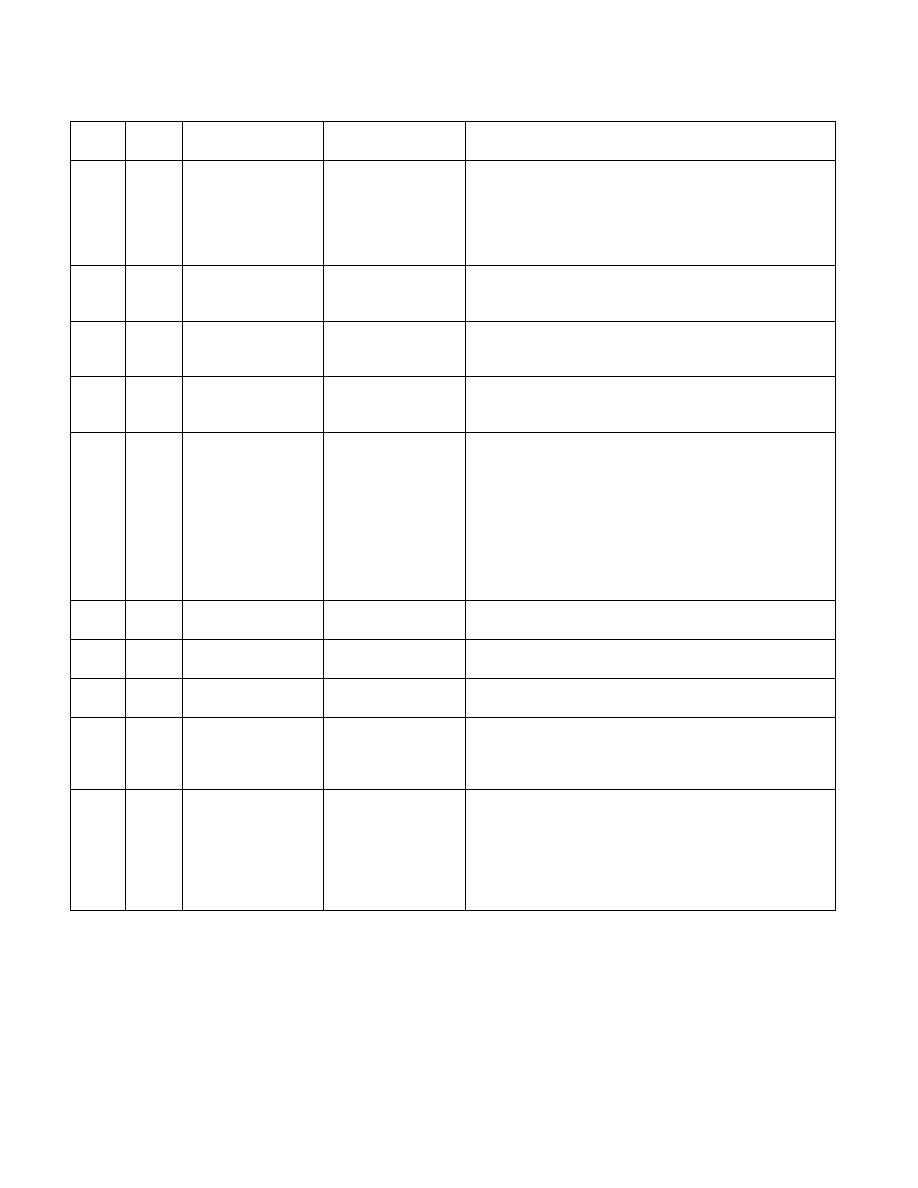

Vol. 3B 19-167

PERFORMANCE-MONITORING EVENTS

CAH

08H

SIMD_COMP_INST_RET

IRED.SCALAR_DOUBLE

Retired computational

Streaming SIMD

Extensions 2 (SSE2)

scalar-double

instructions.

This event counts the number of computational SSE2 scalar-

double instructions retired. Computational instructions perform

arithmetic computations, like add, multiply and divide.

Instructions that perform load and store operations or logical

operations, like XOR, OR, and AND are not counted by this

event.

CBH

01H

MEM_LOAD_RETIRED.L

2_HIT

Retired loads that hit

the L2 cache (precise

event).

This event counts the number of retired load operations that

missed the L1 data cache and hit the L2 cache.

CBH

02H

MEM_LOAD_RETIRED.L

2_MISS

Retired loads that miss

the L2 cache (precise

event).

This event counts the number of retired load operations that

missed the L2 cache.

CBH

04H

MEM_LOAD_RETIRED.D

TLB_MISS

Retired loads that miss

the DTLB (precise

event).

This event counts the number of retired loads that missed the

DTLB. The DTLB miss is not counted if the load operation causes

a fault.

CDH

00H

SIMD_ASSIST

SIMD assists invoked.

This event counts the number of SIMD assists invoked. SIMD

assists are invoked when an EMMS instruction is executed after

MMX™ technology code has changed the MMX state in the

floating point stack. For example, these assists are required in

the following cases.

Streaming SIMD Extensions (SSE) instructions:

1. Denormal input when the DAZ (Denormals Are Zeros) flag is

off.

2. Underflow result when the FTZ (Flush To Zero) flag is off.

CEH

00H

SIMD_INSTR_RETIRED SIMD Instructions

retired.

This event counts the number of SIMD instructions that retired.

CFH

00H

SIMD_SAT_INSTR_RETI

RED

Saturated arithmetic

instructions retired.

This event counts the number of saturated arithmetic SIMD

instructions that retired.

E0H

01H

BR_INST_DECODED

Branch instructions

decoded.

This event counts the number of branch instructions decoded.

E4H

01H

BOGUS_BR

Bogus branches.

This event counts the number of byte sequences that were

mistakenly detected as taken branch instructions. This results

in a BACLEAR event and the BTB is flushed. This occurs mainly

after task switches.

E6H

01H

BACLEARS.ANY

BACLEARS asserted.

This event counts the number of times the front end is

redirected for a branch prediction, mainly when an early branch

prediction is corrected by other branch handling mechanisms in

the front end. This can occur if the code has many branches

such that they cannot be consumed by the branch predictor.

Each Baclear asserted costs approximately 7 cycles. The effect

on total execution time depends on the surrounding code.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment