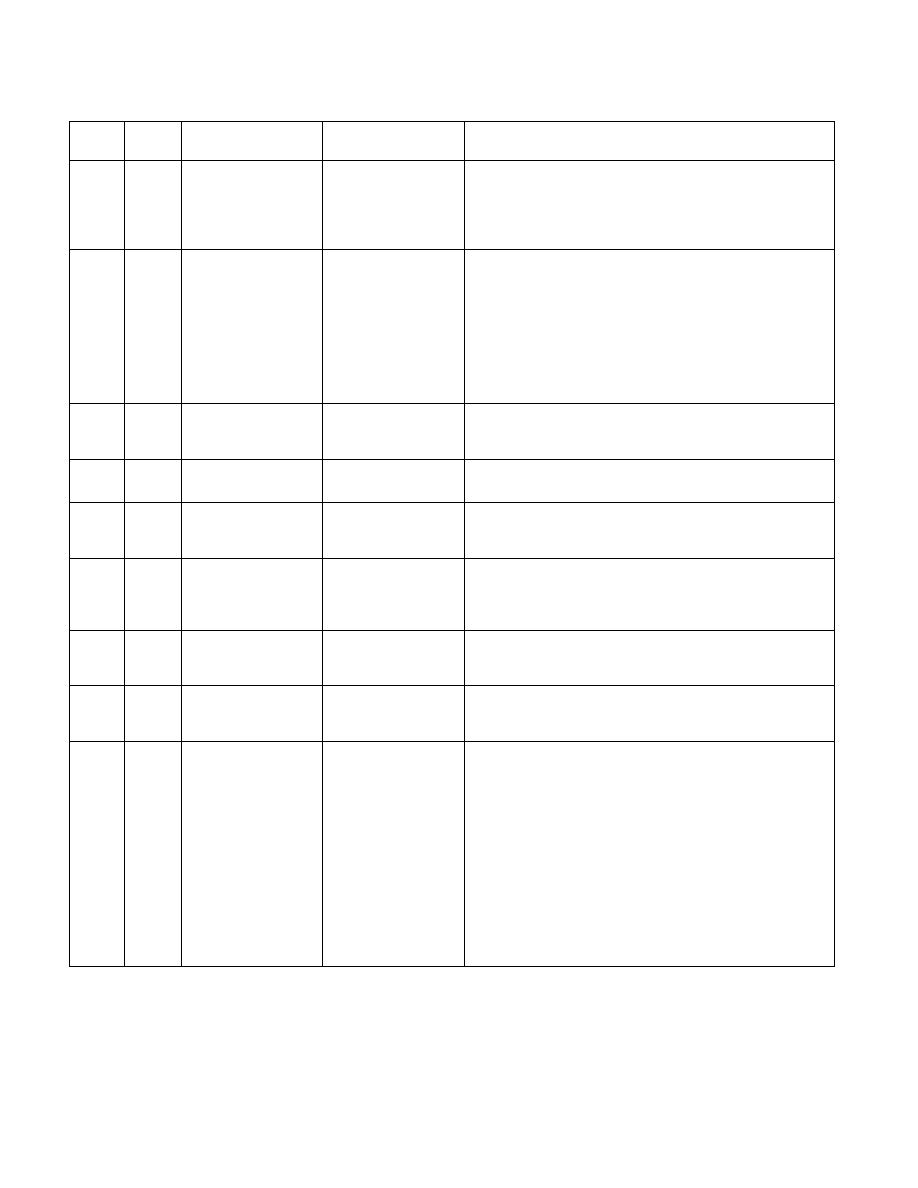

19-164 Vol. 3B

PERFORMANCE-MONITORING EVENTS

N/A

00H

INST_RETIRED.ANY

Instructions retired.

This event counts the number of instructions that retire

execution. For instructions that consist of multiple micro-ops,

this event counts the retirement of the last micro-op of the

instruction. The counter continues counting during hardware

interrupts, traps, and inside interrupt handlers.

C2H

10H

UOPS_RETIRED.ANY

Micro-ops retired.

This event counts the number of micro-ops retired. The

processor decodes complex macro instructions into a sequence

of simpler micro-ops. Most instructions are composed of one or

two micro-ops. Some instructions are decoded into longer

sequences such as repeat instructions, floating point

transcendental instructions, and assists. In some cases micro-op

sequences are fused or whole instructions are fused into one

micro-op. See other UOPS_RETIRED events for differentiating

retired fused and non-fused micro-ops.

C3H

01H

MACHINE_CLEARS.SMC Self-Modifying Code

detected.

This event counts the number of times that a program writes to

a code section. Self-modifying code causes a severe penalty in

all Intel® architecture processors.

C4H

00H

BR_INST_RETIRED.AN

Y

Retired branch

instructions.

This event counts the number of branch instructions retired.

This is an architectural performance event.

C4H

01H

BR_INST_RETIRED.PRE

D_NOT_TAKEN

Retired branch

instructions that were

predicted not-taken.

This event counts the number of branch instructions retired

that were correctly predicted to be not-taken.

C4H

02H

BR_INST_RETIRED.MIS

PRED_NOT_TAKEN

Retired branch

instructions that were

mispredicted not-

taken.

This event counts the number of branch instructions retired

that were mispredicted and not-taken.

C4H

04H

BR_INST_RETIRED.PRE

D_TAKEN

Retired branch

instructions that were

predicted taken.

This event counts the number of branch instructions retired

that were correctly predicted to be taken.

C4H

08H

BR_INST_RETIRED.MIS

PRED_TAKEN

Retired branch

instructions that were

mispredicted taken.

This event counts the number of branch instructions retired

that were mispredicted and taken.

C4H

0AH

BR_INST_RETIRED.MIS

PRED

Retired mispredicted

branch instructions

(precise event).

This event counts the number of retired branch instructions

that were mispredicted by the processor. A branch

misprediction occurs when the processor predicts that the

branch would be taken, but it is not, or vice-versa. Mispredicted

branches degrade the performance because the processor

starts executing instructions along a wrong path it predicts.

When the misprediction is discovered, all the instructions

executed in the wrong path must be discarded, and the

processor must start again on the correct path.

Using the Profile-Guided Optimization (PGO) features of the

Intel® C++ compiler may help reduce branch mispredictions. See

the compiler documentation for more information on this

feature.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment