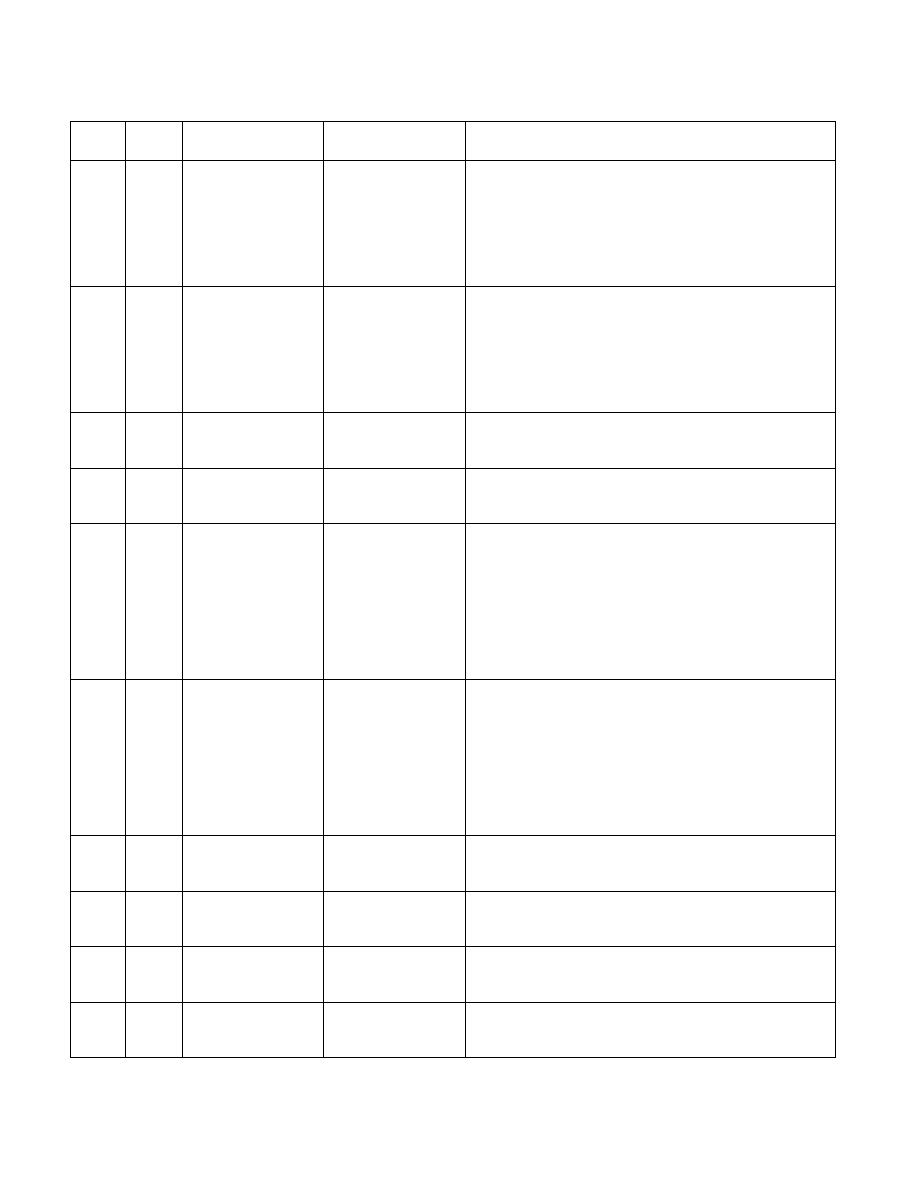

Vol. 3B 19-155

PERFORMANCE-MONITORING EVENTS

0CH

03H

PAGE_WALKS.WALKS

Number of page-walks

executed.

This event counts the number of page-walks executed due to

either a DTLB or ITLB miss. The page walk duration,

PAGE_WALKS.CYCLES, divided by number of page walks is the

average duration of a page walk. This can hint to whether most

of the page-walks are satisfied by the caches or cause an L2

cache miss.

Edge trigger bit must be set.

0CH

03H

PAGE_WALKS.CYCLES

Duration of page-walks

in core cycles.

This event counts the duration of page-walks in core cycles. The

paging mode in use typically affects the duration of page walks.

Page walk duration divided by number of page walks is the

average duration of page-walks. This can hint at whether most

of the page-walks are satisfied by the caches or cause an L2

cache miss.

Edge trigger bit must be cleared.

10H

01H

X87_COMP_OPS_EXE.

ANY.S

Floating point

computational micro-

ops executed.

This event counts the number of x87 floating point

computational micro-ops executed.

10H

81H

X87_COMP_OPS_EXE.

ANY.AR

Floating point

computational micro-

ops retired.

This event counts the number of x87 floating point

computational micro-ops retired.

11H

01H

FP_ASSIST

Floating point assists.

This event counts the number of floating point operations

executed that required micro-code assist intervention. These

assists are required in the following cases.

X87 instructions:

1. NaN or denormal are loaded to a register or used as input

from memory.

2. Division by 0.

3. Underflow output.

11H

81H

FP_ASSIST.AR

Floating point assists.

This event counts the number of floating point operations

executed that required micro-code assist intervention. These

assists are required in the following cases.

X87 instructions:

1. NaN or denormal are loaded to a register or used as input

from memory.

2. Division by 0.

3. Underflow output.

12H

01H

MUL.S

Multiply operations

executed.

This event counts the number of multiply operations executed.

This includes integer as well as floating point multiply

operations.

12H

81H

MUL.AR

Multiply operations

retired.

This event counts the number of multiply operations retired.

This includes integer as well as floating point multiply

operations.

13H

01H

DIV.S

Divide operations

executed.

This event counts the number of divide operations executed.

This includes integer divides, floating point divides and square-

root operations executed.

13H

81H

DIV.AR

Divide operations

retired.

This event counts the number of divide operations retired. This

includes integer divides, floating point divides and square-root

operations executed.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment