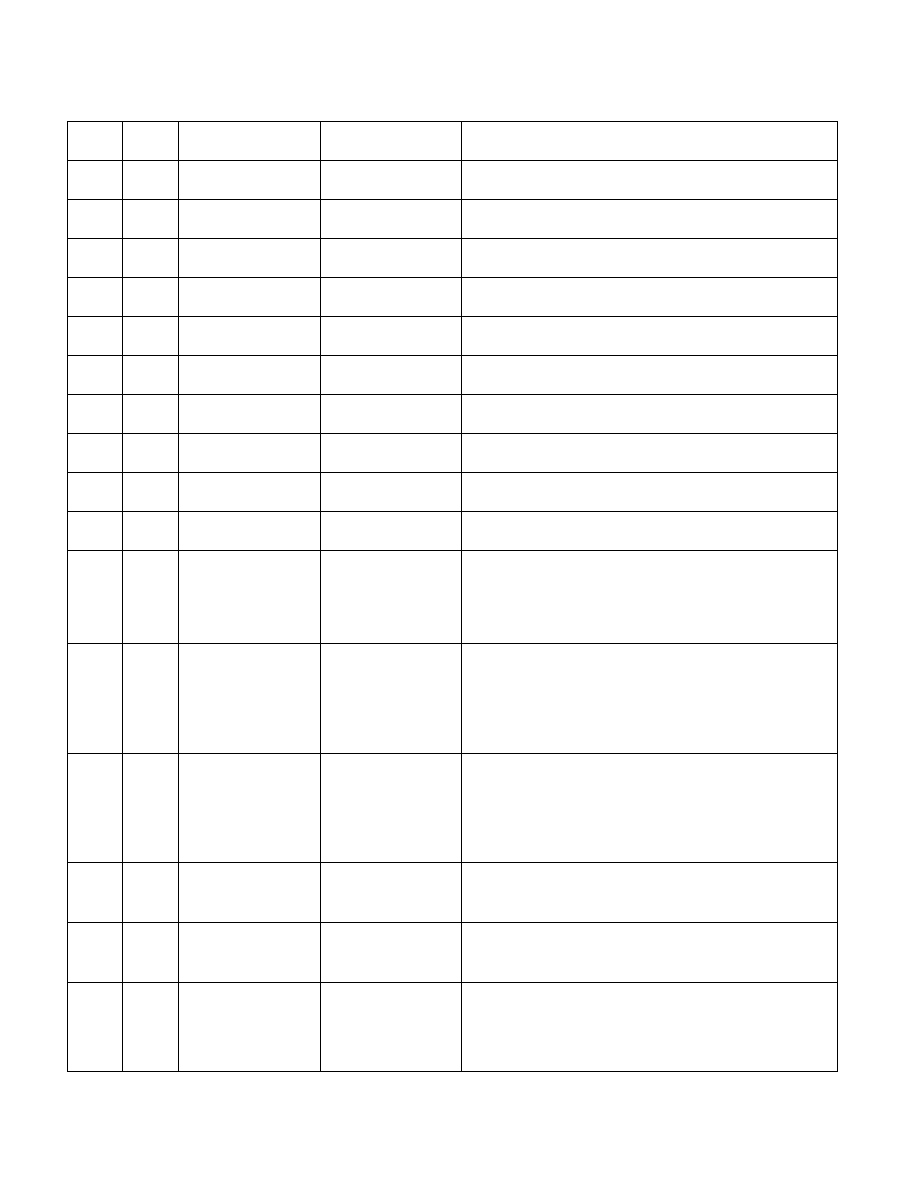

19-150 Vol. 3B

PERFORMANCE-MONITORING EVENTS

03

H

40

H

REHABQ.ANY_LD

Any reissued load uops. This event counts the number of load uops reissued from

Rehabq.

03

H

80

H

REHABQ.ANY_ST

Any reissued store

uops.

This event counts the number of store uops reissued from

Rehabq.

04H

01H

MEM_UOPS_RETIRED.L

1_MISS_LOADS

Loads retired that

missed L1 data cache.

This event counts the number of load ops retired that miss in L1

Data cache. Note that prefetch misses will not be counted.

04H

02H

MEM_UOPS_RETIRED.L

2_HIT_LOADS

Loads retired that hit

L2.

This event counts the number of load micro-ops retired that hit

L2.

04H

04H

MEM_UOPS_RETIRED.L

2_MISS_LOADS

Loads retired that

missed L2.

This event counts the number of load micro-ops retired that

missed L2.

04H

08H

MEM_UOPS_RETIRED.

DTLB_MISS_LOADS

Loads missed DTLB.

This event counts the number of load ops retired that had DTLB

miss.

04H

10H

MEM_UOPS_RETIRED.

UTLB_MISS

Loads missed UTLB.

This event counts the number of load ops retired that had UTLB

miss.

04H

20H

MEM_UOPS_RETIRED.

HITM

Cross core or cross

module hitm.

This event counts the number of load ops retired that got data

from the other core or from the other module.

04H

40H

MEM_UOPS_RETIRED.

ALL_LOADS

All Loads.

This event counts the number of load ops retired.

04H

80H

MEM_UOP_RETIRED.A

LL_STORES

All Stores.

This event counts the number of store ops retired.

05H

01H

PAGE_WALKS.D_SIDE_

CYCLES

Duration of D-side

page-walks in core

cycles.

This event counts every cycle when a D-side (walks due to a

load) page walk is in progress. Page walk duration divided by

number of page walks is the average duration of page-walks.

Edge trigger bit must be cleared. Set Edge to count the number

of page walks.

05H

02H

PAGE_WALKS.I_SIDE_C

YCLES

Duration of I-side page-

walks in core cycles.

This event counts every cycle when an I-side (walks due to an

instruction fetch) page walk is in progress. Page walk duration

divided by number of page walks is the average duration of

page-walks.

Edge trigger bit must be cleared. Set Edge to count the number

of page walks.

05H

03H

PAGE_WALKS.WALKS

Total number of page-

walks that are

completed (I-side and

D-side).

This event counts when a data (D) page walk or an instruction (I)

page walk is completed or started. Since a page walk implies a

TLB miss, the number of TLB misses can be counted by counting

the number of pagewalks.

Edge trigger bit must be set. Clear Edge to count the number of

cycles.

2EH

41H

LONGEST_LAT_CACHE.

MISS

L2 cache request

misses.

This event counts the total number of L2 cache references and

the number of L2 cache misses respectively.

L3 is not supported in Silvermont microarchitecture.

2EH

4FH

LONGEST_LAT_CACHE.

REFERENCE

L2 cache requests

from this core.

This event counts requests originating from the core that

references a cache line in the L2 cache.

L3 is not supported in Silvermont microarchitecture.

30H

00H

L2_REJECT_XQ.ALL

Counts the number of

request from the L2

that were not accepted

into the XQ.

This event counts the number of demand and prefetch

transactions that the L2 XQ rejects due to a full or near full

condition which likely indicates back pressure from the IDI link.

The XQ may reject transactions from the L2Q (non-cacheable

requests), BBS (L2 misses) and WOB (L2 write-back victims).

Table 19-25. Performance Events for Silvermont Microarchitecture

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment