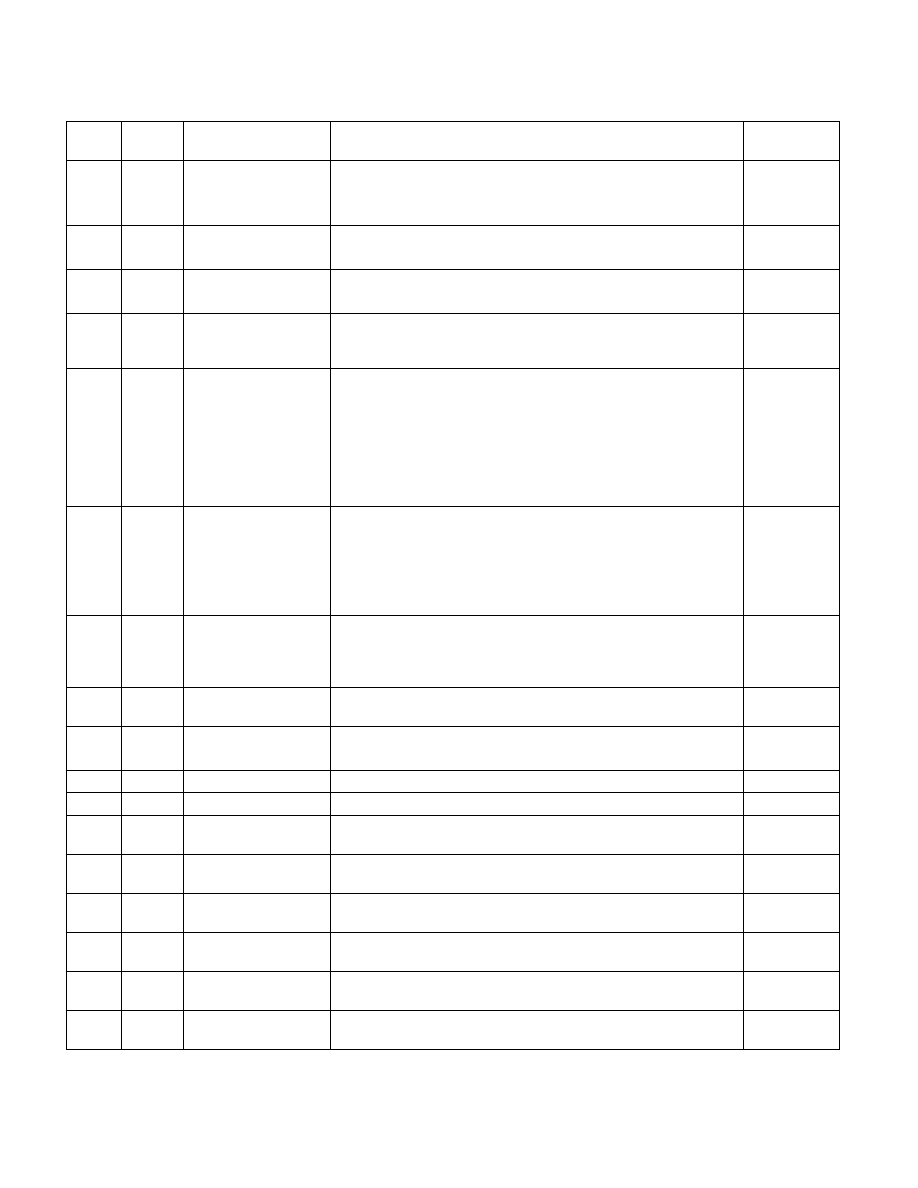

Vol. 3B 19-147

PERFORMANCE-MONITORING EVENTS

C5H

FEH

BR_MISP_RETIRED.TAK

EN_JCC

Counts mispredicted retired Jcc (Jump on Conditional Code/Jump if

Condition is Met) branch instructions retired that were supposed to be

taken but the processor predicted that it would not be taken.

Precise Event

C5H

FBH

BR_MISP_RETIRED.IND_

CALL

Counts mispredicted near indirect CALL branch instructions retired,

where the target address taken was not what the processor predicted.

Precise Event

C5H

F7H

BR_MISP_RETIRED.RET

URN

Counts mispredicted near RET branch instructions retired, where the

return address taken was not what the processor predicted.

Precise Event

C5H

EBH

BR_MISP_RETIRED.NON

_RETURN_IND

Counts mispredicted branch instructions retired that were near indirect

call or near indirect jmp, where the target address taken was not what

the processor predicted.

Precise Event

CAH

01H

ISSUE_SLOTS_NOT_CO

NSUMED.RESOURCE_FU

LL

Counts the number of issue slots per core cycle that were not

consumed because of a full resource in the back end. Including but not

limited to resources include the Re-order Buffer (ROB), reservation

stations (RS), load/store buffers, physical registers, or any other

needed machine resource that is currently unavailable. Note that uops

must be available for consumption in order for this event to fire. If a

uop is not available (Instruction Queue is empty), this event will not

count.

CAH

02H

ISSUE_SLOTS_NOT_CO

NSUMED.RECOVERY

Counts the number of issue slots per core cycle that were not

consumed by the back end because allocation is stalled waiting for a

mispredicted jump to retire or other branch-like conditions (e.g. the

event is relevant during certain microcode flows). Counts all issue slots

blocked while within this window, including slots where uops were not

available in the Instruction Queue.

CAH

00H

ISSUE_SLOTS_NOT_CO

NSUMED.ANY

Counts the number of issue slots per core cycle that were not

consumed by the back end due to either a full resource in the back end

(RESOURCE_FULL), or due to the processor recovering from some

event (RECOVERY).

CBH

01H

HW_INTERRUPTS.RECEI

VED

Counts hardware interrupts received by the processor.

CBH

04H

HW_INTERRUPTS.PENDI

NG_AND_MASKED

Counts core cycles during which there are pending interrupts, but

interrupts are masked (EFLAGS.IF = 0).

CDH

00H

CYCLES_DIV_BUSY.ALL Counts core cycles if either divide unit is busy.

CDH

01H

CYCLES_DIV_BUSY.IDIV Counts core cycles if the integer divide unit is busy.

CDH

02H

CYCLES_DIV_BUSY.FPDI

V

Counts core cycles if the floating point divide unit is busy.

D0H

81H

MEM_UOPS_RETIRED.A

LL_LOADS

Counts the number of load uops retired.

Precise Event

D0H

82H

MEM_UOPS_RETIRED.A

LL_STORES

Counts the number of store uops retired.

Precise Event

D0H

83H

MEM_UOPS_RETIRED.A

LL

Counts the number of memory uops retired that are either a load or a

store or both.

Precise Event

D0H

11H

MEM_UOPS_RETIRED.D

TLB_MISS_LOADS

Counts load uops retired that caused a DTLB miss.

Precise Event

D0H

12H

MEM_UOPS_RETIRED.D

TLB_MISS_STORES

Counts store uops retired that caused a DTLB miss.

Precise Event

Table 19-24. Non-Architectural Performance Events for the Goldmont Microarchitecture (Contd.)

Event

Num.

Umask

Value

Event Name

Description

Comment