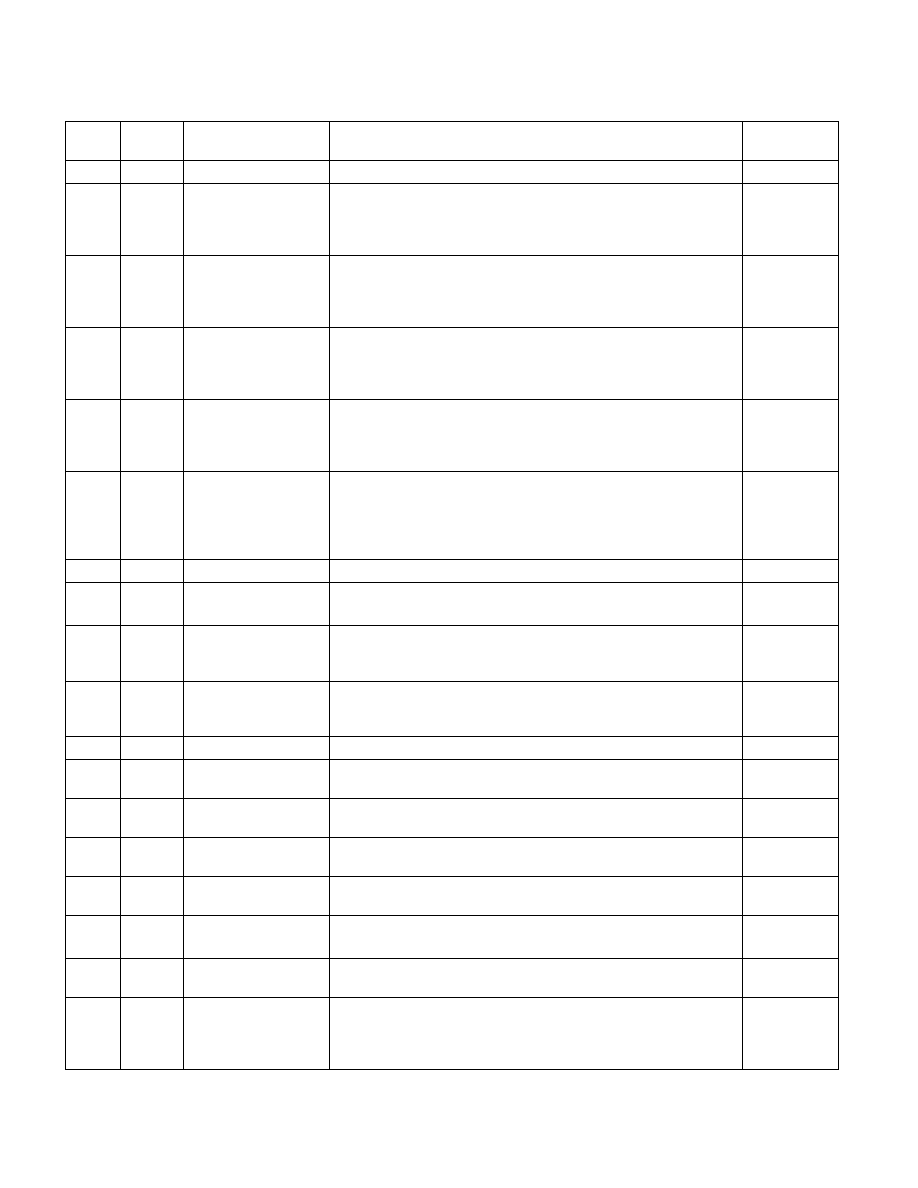

19-146 Vol. 3B

PERFORMANCE-MONITORING EVENTS

C2H

00H

UOPS_RETIRED.ANY

Counts uops which have retired.

Precise Event

C2H

01H

UOPS_RETIRED.MS

Counts uops retired that are from the complex flows issued by the

micro-sequencer (MS). Counts both the uops from a micro-coded

instruction, and the uops that might be generated from a micro-coded

assist.

Precise Event

C3H

01H

MACHINE_CLEARS.SMC Counts the number of times that the processor detects that a program

is writing to a code section and has to perform a machine clear because

of that modification. Self-modifying code (SMC) causes a severe penalty

in all Intel architecture processors.

C3H

02H

MACHINE_CLEARS.MEM

ORY_ORDERING

Counts machine clears due to memory ordering issues. This occurs

when a snoop request happens and the machine is uncertain if memory

ordering will be preserved as another core is in the process of

modifying the data.

C3H

04H

MACHINE_CLEARS.FP_A

SSIST

Counts machine clears due to floating-point (FP) operations needing

assists. For instance, if the result was a floating-point denormal, the

hardware clears the pipeline and reissues uops to produce the correct

IEEE compliant denormal result.

C3H

08H

MACHINE_CLEARS.DISA

MBIGUATION

Counts machine clears due to memory disambiguation. Memory

disambiguation happens when a load which has been issued conflicts

with a previous un-retired store in the pipeline whose address was not

known at issue time, but is later resolved to be the same as the load

address.

C3H

00H

MACHINE_CLEARS.ALL

Counts machine clears for any reason.

C4H

00H

BR_INST_RETIRED.ALL_

BRANCHES

Counts branch instructions retired for all branch types. This is an

architectural performance event.

Precise Event

C4H

7EH

BR_INST_RETIRED.JCC

Counts retired Jcc (Jump on Conditional Code/Jump if Condition is Met)

branch instructions retired, including both when the branch was taken

and when it was not taken.

Precise Event

C4H

FEH

BR_INST_RETIRED.TAK

EN_JCC

Counts Jcc (Jump on Conditional Code/Jump if Condition is Met) branch

instructions retired that were taken and does not count when the Jcc

branch instruction were not taken.

Precise Event

C4H

F9H

BR_INST_RETIRED.CALL Counts near CALL branch instructions retired.

Precise Event

C4H

FDH

BR_INST_RETIRED.REL_

CALL

Counts near relative CALL branch instructions retired.

Precise Event

C4H

FBH

BR_INST_RETIRED.IND_

CALL

Counts near indirect CALL branch instructions retired.

Precise Event

C4H

F7H

BR_INST_RETIRED.RET

URN

Counts near return branch instructions retired.

Precise Event

C4H

EBH

BR_INST_RETIRED.NON

_RETURN_IND

Counts near indirect call or near indirect jmp branch instructions retired. Precise Event

C4H

BFH

BR_INST_RETIRED.FAR

_BRANCH

Counts far branch instructions retired. This includes far jump, far call

and return, and Interrupt call and return.

Precise Event

C5H

00H

BR_MISP_RETIRED.ALL

_BRANCHES

Counts mispredicted branch instructions retired including all branch

types.

Precise Event

C5H

7EH

BR_MISP_RETIRED.JCC

Counts mispredicted retired Jcc (Jump on Conditional Code/Jump if

Condition is Met) branch instructions retired, including both when the

branch was supposed to be taken and when it was not supposed to be

taken (but the processor predicted the opposite condition).

Precise Event

Table 19-24. Non-Architectural Performance Events for the Goldmont Microarchitecture (Contd.)

Event

Num.

Umask

Value

Event Name

Description

Comment