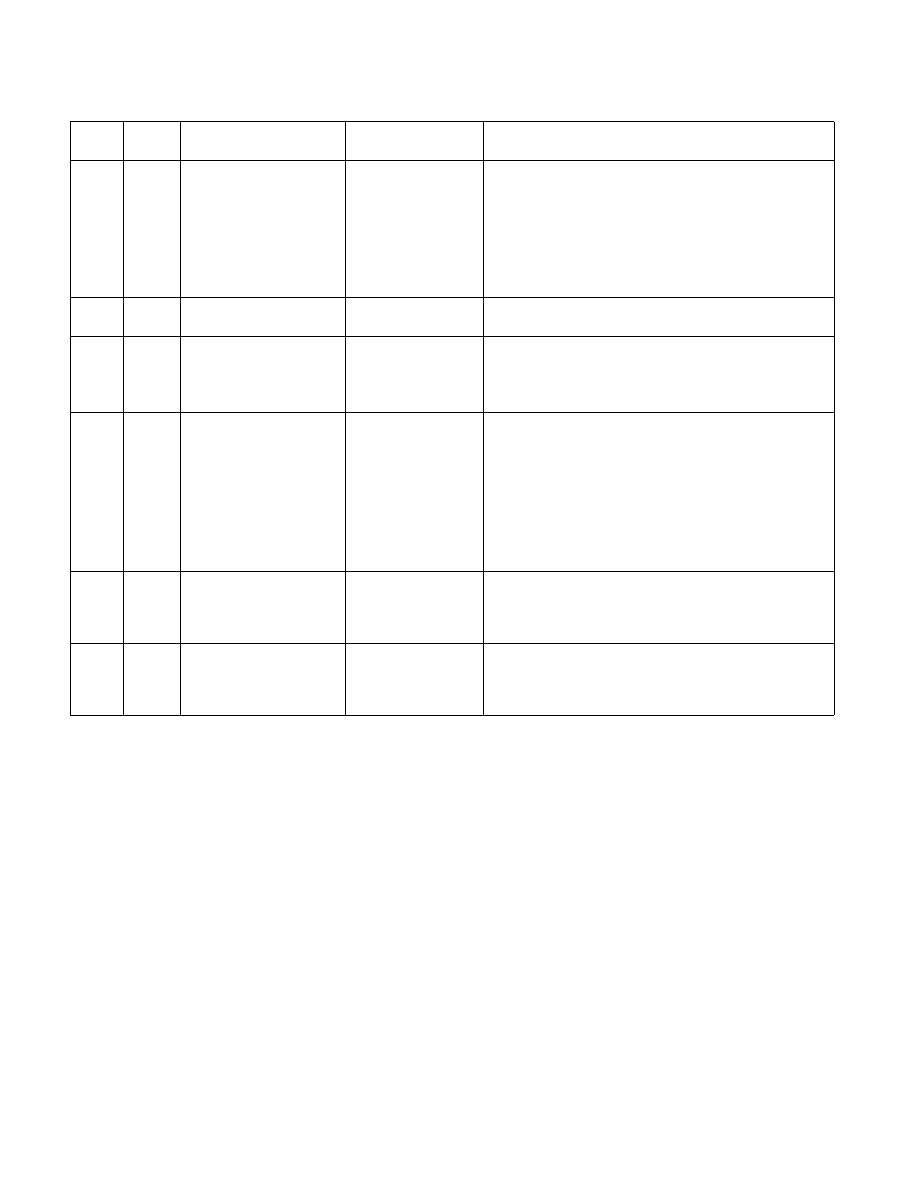

19-142 Vol. 3B

PERFORMANCE-MONITORING EVENTS

DCH

1FH

RESOURCE_

STALLS.ANY

Resource related

stalls.

This event counts the number of cycles while resource-

related stalls occurs for any conditions described by the

following events:

• RESOURCE_STALLS.ROB_FULL

• RESOURCE_STALLS.RS_FULL

• RESOURCE_STALLS.LD_ST

• RESOURCE_STALLS.FPCW

• RESOURCE_STALLS.BR_MISS_CLEAR

E0H

00H

BR_INST_

DECODED

Branch instructions

decoded.

This event counts the number of branch instructions

decoded.

E4H

00H

BOGUS_BR

Bogus branches.

This event counts the number of byte sequences that were

mistakenly detected as taken branch instructions.

This results in a BACLEAR event. This occurs mainly after

task switches.

E6H

00H

BACLEARS

BACLEARS asserted.

This event counts the number of times the front end is

resteered, mainly when the BPU cannot provide a correct

prediction and this is corrected by other branch handling

mechanisms at the front and. This can occur if the code has

many branches such that they cannot be consumed by the

BPU.

Each BACLEAR asserted costs approximately 7 cycles of

instruction fetch. The effect on total execution time

depends on the surrounding code.

F0H

00H

PREF_RQSTS_UP

Upward prefetches

issued from DPL.

This event counts the number of upward prefetches issued

from the Data Prefetch Logic (DPL) to the L2 cache. A

prefetch request issued to the L2 cache cannot be cancelled

and the requested cache line is fetched to the L2 cache.

F8H

00H

PREF_RQSTS_DN

Downward prefetches

issued from DPL.

This event counts the number of downward prefetches

issued from the Data Prefetch Logic (DPL) to the L2 cache. A

prefetch request issued to the L2 cache cannot be cancelled

and the requested cache line is fetched to the L2 cache.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment