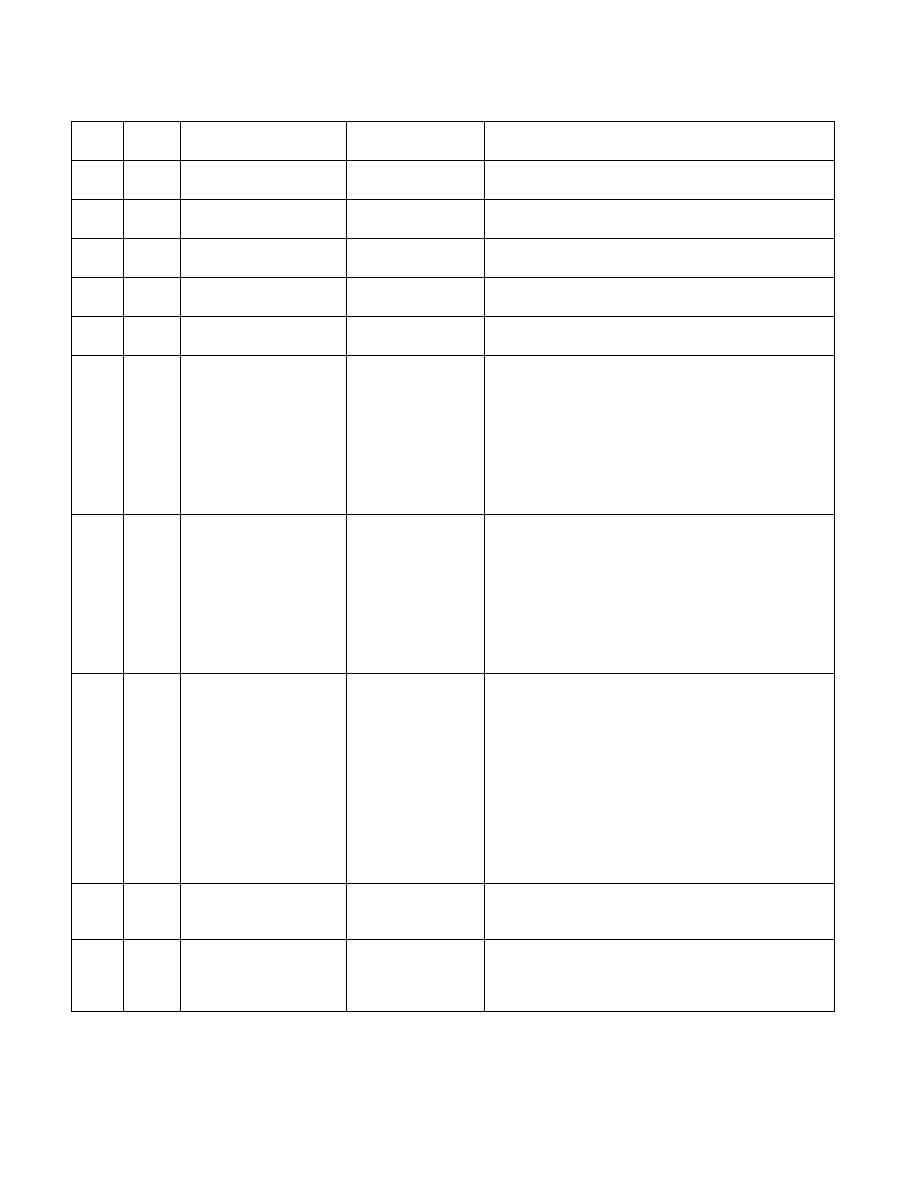

Vol. 3B 19-141

PERFORMANCE-MONITORING EVENTS

D5H

01H

SEG_REG_

RENAMES.ES

Segment renames -

ES.

This event counts the number of times the ES segment

register is renamed.

D5H

02H

SEG_REG_

RENAMES.DS

Segment renames -

DS.

This event counts the number of times the DS segment

register is renamed.

D5H

04H

SEG_REG_

RENAMES.FS

Segment renames -

FS.

This event counts the number of times the FS segment

register is renamed.

D5H

08H

SEG_REG_

RENAMES.GS

Segment renames -

GS.

This event counts the number of times the GS segment

register is renamed.

D5H

0FH

SEG_REG_

RENAMES.ANY

Any (ES/DS/FS/GS)

segment rename.

This event counts the number of times any of the four

segment registers (ES/DS/FS/GS) is renamed.

DCH

01H

RESOURCE_

STALLS.ROB_FULL

Cycles during which

the ROB full.

This event counts the number of cycles when the number of

instructions in the pipeline waiting for retirement reaches

the limit the processor can handle.

A high count for this event indicates that there are long

latency operations in the pipe (possibly load and store

operations that miss the L2 cache, and other instructions

that depend on these cannot execute until the former

instructions complete execution). In this situation new

instructions cannot enter the pipe and start execution.

DCH

02H

RESOURCE_

STALLS.RS_FULL

Cycles during which

the RS full.

This event counts the number of cycles when the number of

instructions in the pipeline waiting for execution reaches

the limit the processor can handle.

A high count of this event indicates that there are long

latency operations in the pipe (possibly load and store

operations that miss the L2 cache, and other instructions

that depend on these cannot execute until the former

instructions complete execution). In this situation new

instructions cannot enter the pipe and start execution.

DCH

04

RESOURCE_

STALLS.LD_ST

Cycles during which

the pipeline has

exceeded load or store

limit or waiting to

commit all stores.

This event counts the number of cycles while resource-

related stalls occur due to:

• The number of load instructions in the pipeline reached

the limit the processor can handle. The stall ends when a

loading instruction retires.

• The number of store instructions in the pipeline reached

the limit the processor can handle. The stall ends when a

storing instruction commits its data to the cache or

memory.

• There is an instruction in the pipe that can be executed

only when all previous stores complete and their data is

committed in the caches or memory. For example, the

SFENCE and MFENCE instructions require this behavior.

DCH

08H

RESOURCE_

STALLS.FPCW

Cycles stalled due to

FPU control word

write.

This event counts the number of cycles while execution was

stalled due to writing the floating-point unit (FPU) control

word.

DCH

10H

RESOURCE_

STALLS.BR_MISS_CLEAR

Cycles stalled due to

branch misprediction.

This event counts the number of cycles after a branch

misprediction is detected at execution until the branch and

all older micro-ops retire. During this time new micro-ops

cannot enter the out-of-order pipeline.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment