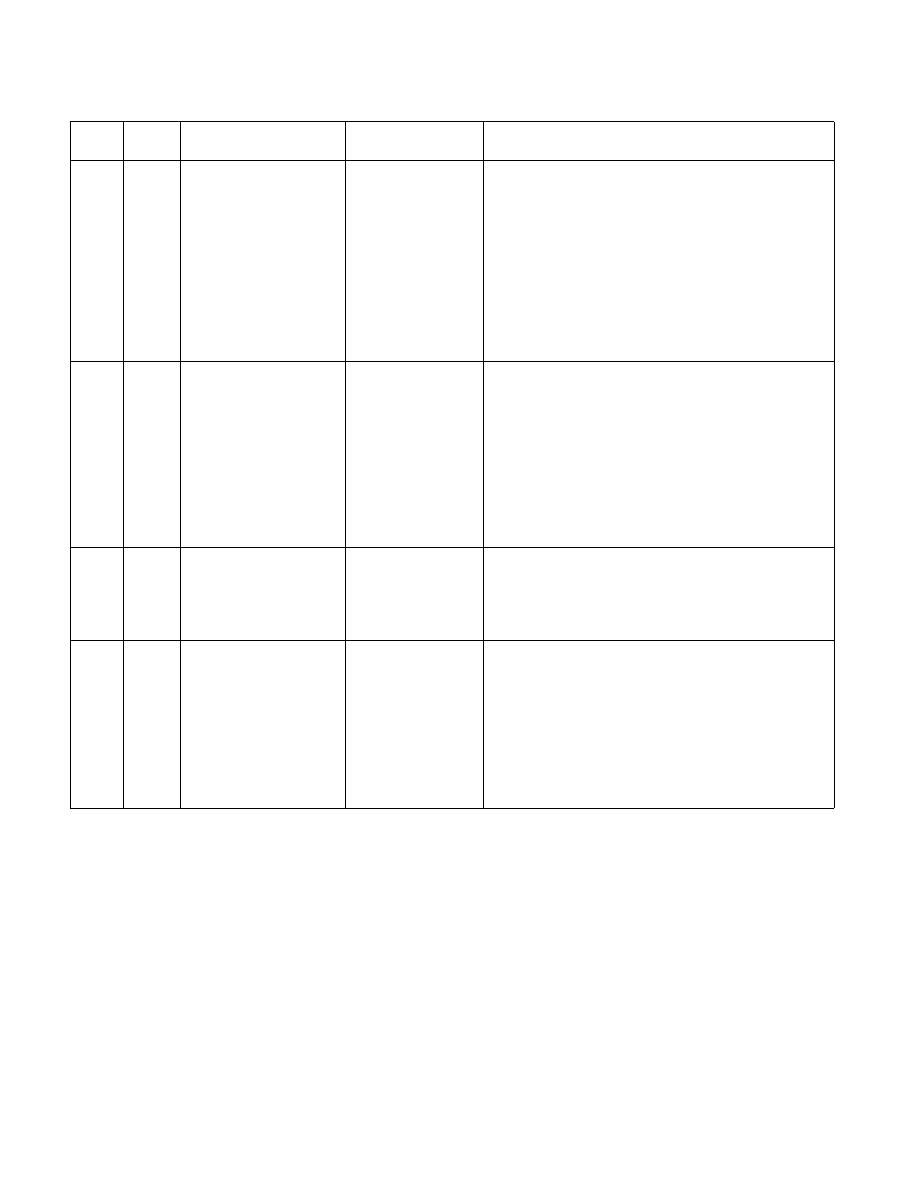

19-138 Vol. 3B

PERFORMANCE-MONITORING EVENTS

CBH

01H

MEM_LOAD_

RETIRED.L1D

_MISS

Retired loads that miss

the L1 data cache

(precise event).

This event counts the number of retired load operations

that missed the L1 data cache. This includes loads from

cache lines that are currently being fetched, due to a

previous L1 data cache miss to the same cache line.

This event counts loads from cacheable memory only. The

event does not count loads by software prefetches.

When this event is captured with the precise event

mechanism, the collected samples contain the address of

the instruction that was executed immediately after the

instruction that caused the event.

Use IA32_PMC0 only.

CBH

02H

MEM_LOAD_

RETIRED.L1D_

LINE_MISS

L1 data cache line

missed by retired

loads (precise event).

This event counts the number of load operations that miss

the L1 data cache and send a request to the L2 cache to

fetch the missing cache line. That is the missing cache line

fetching has not yet started.

The event count is equal to the number of cache lines

fetched from the L2 cache by retired loads.

This event counts loads from cacheable memory only. The

event does not count loads by software prefetches.

The event might not be counted if the load is blocked (see

LOAD_BLOCK events).

When this event is captured with the precise event

mechanism, the collected samples contain the address of

the instruction that was executed immediately after the

instruction that caused the event.

Use IA32_PMC0 only.

CBH

04H

MEM_LOAD_

RETIRED.L2_MISS

Retired loads that miss

the L2 cache (precise

event).

This event counts the number of retired load operations

that missed the L2 cache.

This event counts loads from cacheable memory only. It

does not count loads by software prefetches.

When this event is captured with the precise event

mechanism, the collected samples contain the address of

the instruction that was executed immediately after the

instruction that caused the event.

Use IA32_PMC0 only.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment