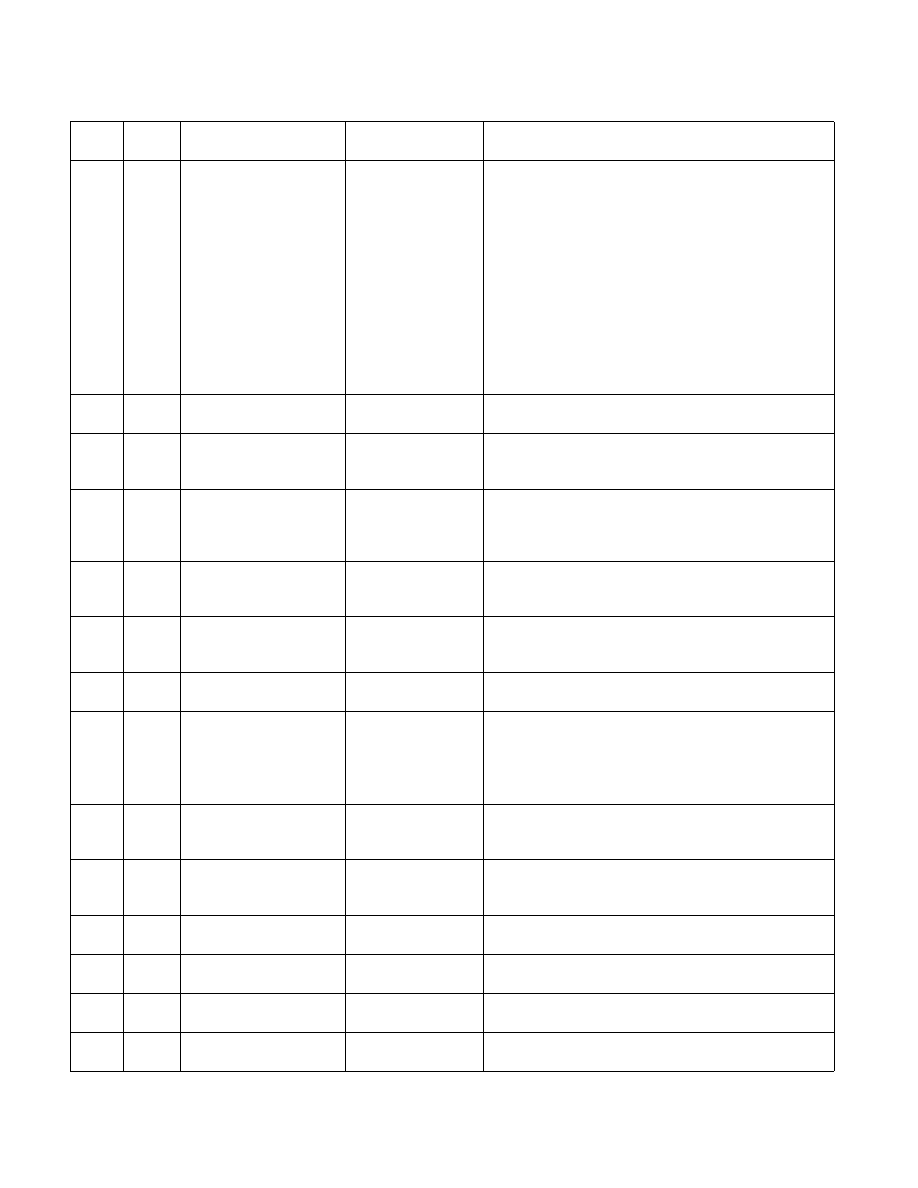

19-136 Vol. 3B

PERFORMANCE-MONITORING EVENTS

C3H

04H

MACHINE_NUKES.MEM_OR

DER

Execution pipeline

restart due to memory

ordering conflict or

memory

disambiguation

misprediction.

This event counts the number of times the pipeline is

restarted due to either multi-threaded memory ordering

conflicts or memory disambiguation misprediction.

A multi-threaded memory ordering conflict occurs when a

store, which is executed in another core, hits a load that is

executed out of order in this core but not yet retired. As a

result, the load needs to be restarted to satisfy the memory

ordering model.

See Chapter 8, “Multiple-Processor Management” in the

Intel® 64 and IA-32 Architectures Software Developer’s

Manual, Volume 3A.

To count memory disambiguation mispredictions, use the

event MEMORY_DISAMBIGUATION.RESET.

C4H

00H

BR_INST_RETIRED.ANY

Retired branch

instructions.

This event counts the number of branch instructions retired.

This is an architectural performance event.

C4H

01H

BR_INST_RETIRED.PRED_N

OT_

TAKEN

Retired branch

instructions that were

predicted not-taken.

This event counts the number of branch instructions retired

that were correctly predicted to be not-taken.

C4H

02H

BR_INST_RETIRED.MISPRE

D_NOT_

TAKEN

Retired branch

instructions that were

mispredicted not-

taken.

This event counts the number of branch instructions retired

that were mispredicted and not-taken.

C4H

04H

BR_INST_RETIRED.PRED_T

AKEN

Retired branch

instructions that were

predicted taken.

This event counts the number of branch instructions retired

that were correctly predicted to be taken.

C4H

08H

BR_INST_RETIRED.MISPRE

D_TAKEN

Retired branch

instructions that were

mispredicted taken.

This event counts the number of branch instructions retired

that were mispredicted and taken.

C4H

0CH

BR_INST_RETIRED.TAKEN

Retired taken branch

instructions.

This event counts the number of branches retired that were

taken.

C5H

00H

BR_INST_RETIRED.MISPRE

D

Retired mispredicted

branch instructions.

(precise event)

This event counts the number of retired branch instructions

that were mispredicted by the processor. A branch

misprediction occurs when the processor predicts that the

branch would be taken, but it is not, or vice-versa.

This is an architectural performance event.

C6H

01H

CYCLES_INT_

MASKED

Cycles during which

interrupts are

disabled.

This event counts the number of cycles during which

interrupts are disabled.

C6H

02H

CYCLES_INT_

PENDING_AND

_MASKED

Cycles during which

interrupts are pending

and disabled.

This event counts the number of cycles during which there

are pending interrupts but interrupts are disabled.

C7H

01H

SIMD_INST_

RETIRED.PACKED_SINGLE

Retired SSE packed-

single instructions.

This event counts the number of SSE packed-single

instructions retired.

C7H

02H

SIMD_INST_

RETIRED.SCALAR_SINGLE

Retired SSE scalar-

single instructions.

This event counts the number of SSE scalar-single

instructions retired.

C7H

04H

SIMD_INST_

RETIRED.PACKED_DOUBLE

Retired SSE2 packed-

double instructions.

This event counts the number of SSE2 packed-double

instructions retired.

C7H

08H

SIMD_INST_

RETIRED.SCALAR_DOUBLE

Retired SSE2 scalar-

double instructions.

This event counts the number of SSE2 scalar-double

instructions retired.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment