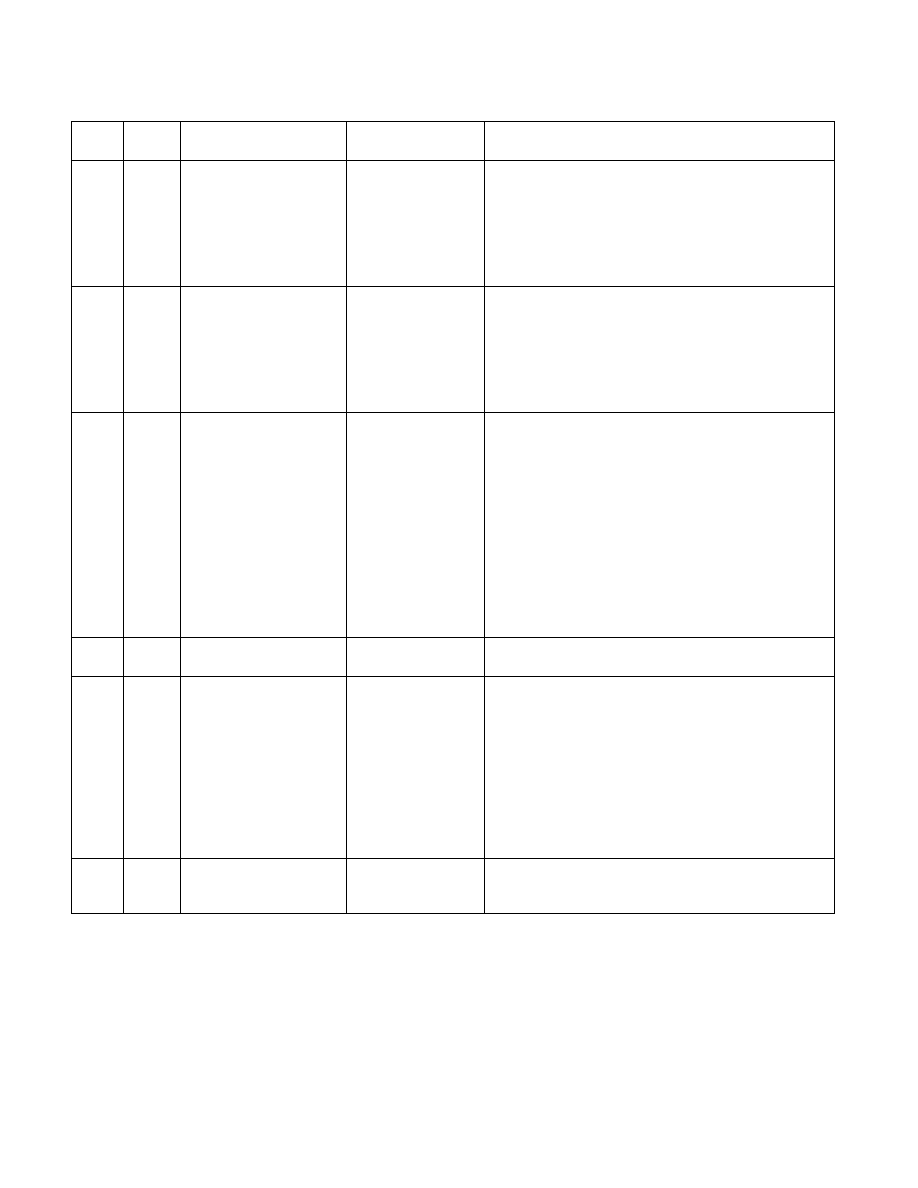

Vol. 3B 19-135

PERFORMANCE-MONITORING EVENTS

C2H

02H

UOPS_RETIRED.

STD_STA

Fused store address +

data retired.

This event counts the number of store address calculations

that are fused with store data emission into one micro-op.

Traditionally, each store operation required two micro-ops.

This event counts fusion of retired micro-ops only. Fusion

decreases the number of micro-ops in the processor

pipeline. A high value for this event count indicates that the

code is using the processor resources effectively.

C2H

04H

UOPS_RETIRED.

MACRO_FUSION

Retired instruction

pairs fused into one

micro-op.

This event counts the number of times CMP or TEST

instructions were fused with a conditional branch

instruction into one micro-op. It counts fusion by retired

micro-ops only.

Fusion decreases the number of micro-ops in the processor

pipeline. A high value for this event count indicates that the

code uses the processor resources more effectively.

C2H

07H

UOPS_RETIRED.

FUSED

Fused micro-ops

retired.

This event counts the total number of retired fused micro-

ops. The counts include the following fusion types:

• Fusion of load operation with an arithmetic operation or

with an indirect branch (counted by event

UOPS_RETIRED.LD_IND_BR)

• Fusion of store address and data (counted by event

UOPS_RETIRED.STD_STA)

• Fusion of CMP or TEST instruction with a conditional

branch instruction (counted by event

UOPS_RETIRED.MACRO_FUSION)

Fusion decreases the number of micro-ops in the processor

pipeline. A high value for this event count indicates that the

code is using the processor resources effectively.

C2H

08H

UOPS_RETIRED.

NON_FUSED

Non-fused micro-ops

retired.

This event counts the number of micro-ops retired that

were not fused.

C2H

0FH

UOPS_RETIRED.

ANY

Micro-ops retired.

This event counts the number of micro-ops retired. The

processor decodes complex macro instructions into a

sequence of simpler micro-ops. Most instructions are

composed of one or two micro-ops.

Some instructions are decoded into longer sequences such

as repeat instructions, floating point transcendental

instructions, and assists. In some cases micro-op sequences

are fused or whole instructions are fused into one micro-op.

See other UOPS_RETIRED events for differentiating retired

fused and non-fused micro-ops.

C3H

01H

MACHINE_

NUKES.SMC

Self-Modifying Code

detected.

This event counts the number of times that a program

writes to a code section. Self-modifying code causes a

severe penalty in all Intel 64 and IA-32 processors.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment