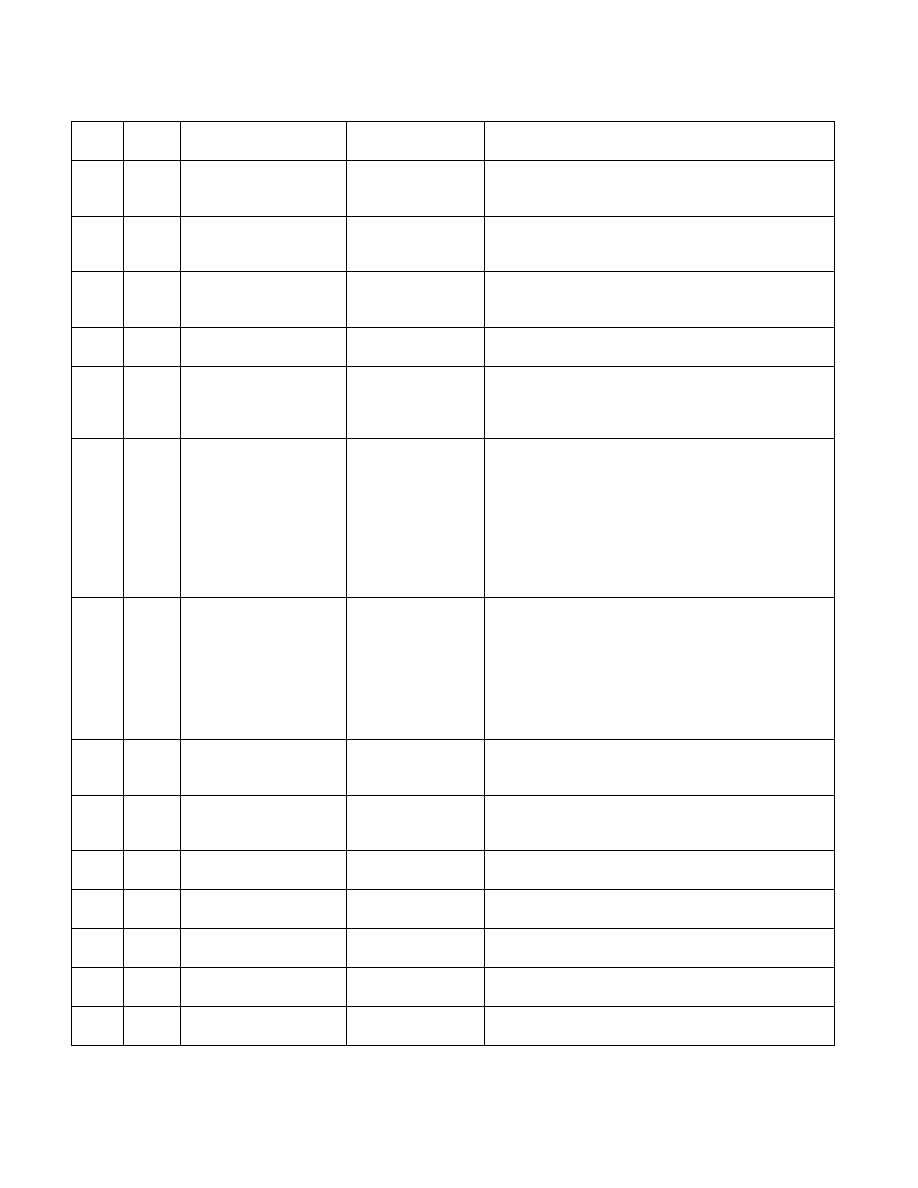

Vol. 3B 19-133

PERFORMANCE-MONITORING EVENTS

A1H

08H

RS_UOPS_

DISPATCHED.PORT3

Cycles micro-ops

dispatched for

execution on port 3.

This event counts the number of cycles for which micro-ops

dispatched for execution. Each cycle, at most one micro-op

can be dispatched on the port. Use IA32_PMC0 only.

A1H

10H

RS_UOPS_

DISPATCHED.PORT4

Cycles micro-ops

dispatched for

execution on port 4.

This event counts the number of cycles for which micro-ops

dispatched for execution. Each cycle, at most one micro-op

can be dispatched on the port. Use IA32_PMC0 only.

A1H

20H

RS_UOPS_

DISPATCHED.PORT5

Cycles micro-ops

dispatched for

execution on port 5.

This event counts the number of cycles for which micro-ops

dispatched for execution. Each cycle, at most one micro-op

can be dispatched on the port. Use IA32_PMC0 only.

AAH

01H

MACRO_INSTS.

DECODED

Instructions decoded.

This event counts the number of instructions decoded (but

not necessarily executed or retired).

AAH

08H

MACRO_INSTS.

CISC_DECODED

CISC Instructions

decoded.

This event counts the number of complex instructions

decoded. Complex instructions usually have more than four

micro-ops. Only one complex instruction can be decoded at a

time.

ABH

01H

ESP.SYNCH

ESP register content

synchron-ization.

This event counts the number of times that the ESP register

is explicitly used in the address expression of a load or store

operation, after it is implicitly used, for example by a push or

a pop instruction.

ESP synch micro-op uses resources from the rename pipe-

stage and up to retirement. The expected ratio of this event

divided by the number of ESP implicit changes is 0,2. If the

ratio is higher, consider rearranging your code to avoid ESP

synchronization events.

ABH

02H

ESP.ADDITIONS

ESP register automatic

additions.

This event counts the number of ESP additions performed

automatically by the decoder. A high count of this event is

good, since each automatic addition performed by the

decoder saves a micro-op from the execution units.

To maximize the number of ESP additions performed

automatically by the decoder, choose instructions that

implicitly use the ESP, such as PUSH, POP, CALL, and RET

instructions whenever possible.

B0H

00H

SIMD_UOPS_EXEC

SIMD micro-ops

executed (excluding

stores).

This event counts all the SIMD micro-ops executed. It does

not count MOVQ and MOVD stores from register to memory.

B1H

00H

SIMD_SAT_UOP_

EXEC

SIMD saturated

arithmetic micro-ops

executed.

This event counts the number of SIMD saturated arithmetic

micro-ops executed.

B3H

01H

SIMD_UOP_

TYPE_EXEC.MUL

SIMD packed multiply

micro-ops executed.

This event counts the number of SIMD packed multiply

micro-ops executed.

B3H

02H

SIMD_UOP_TYPE_EXEC.SHI

FT

SIMD packed shift

micro-ops executed.

This event counts the number of SIMD packed shift micro-

ops executed.

B3H

04H

SIMD_UOP_TYPE_EXEC.PA

CK

SIMD pack micro-ops

executed.

This event counts the number of SIMD pack micro-ops

executed.

B3H

08H

SIMD_UOP_TYPE_EXEC.UN

PACK

SIMD unpack micro-

ops executed.

This event counts the number of SIMD unpack micro-ops

executed.

B3H

10H

SIMD_UOP_TYPE_EXEC.LO

GICAL

SIMD packed logical

micro-ops executed.

This event counts the number of SIMD packed logical micro-

ops executed.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment