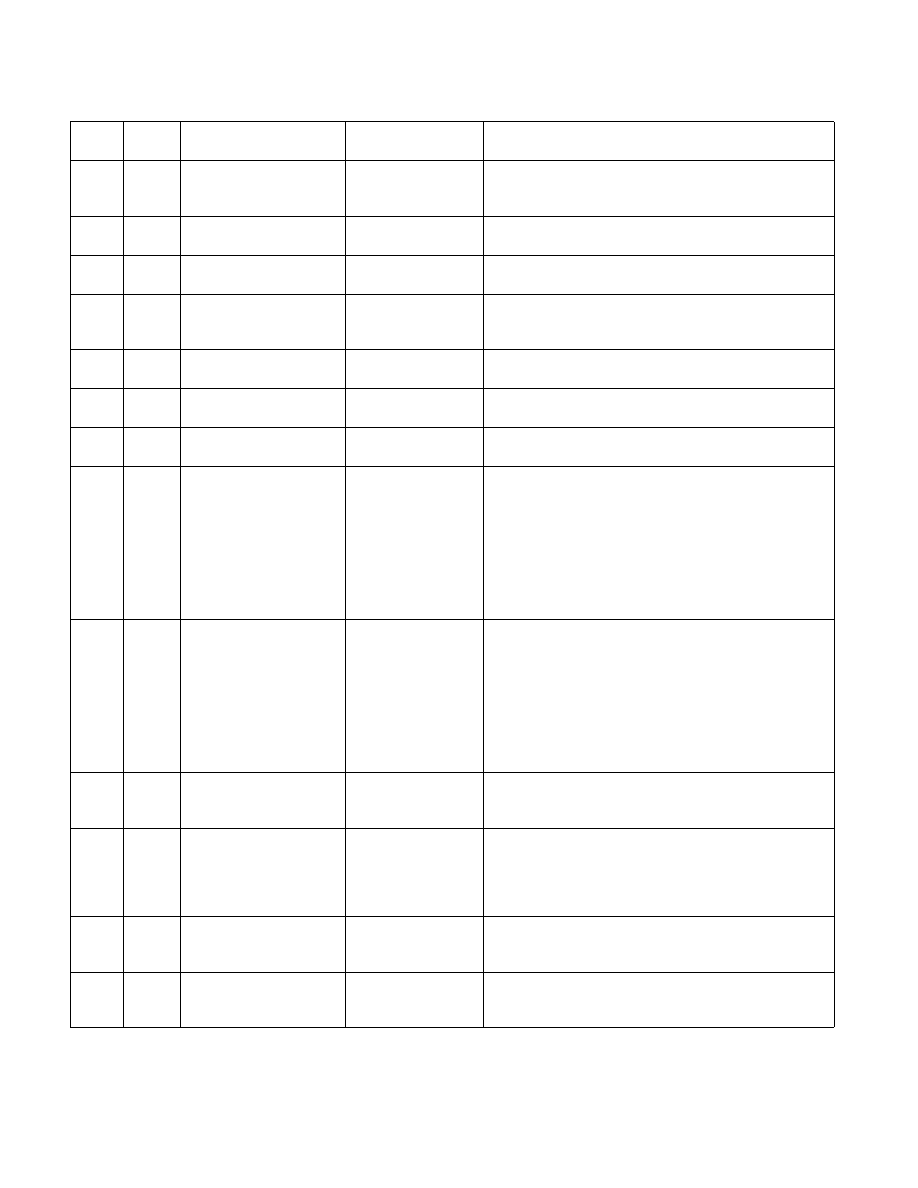

19-132 Vol. 3B

PERFORMANCE-MONITORING EVENTS

8EH

00H

BR_IND_MISSP

_EXEC

Mispredicted indirect

branch instructions

executed.

This event counts the number of mispredicted indirect

branch instructions that were executed.

8FH

00H

BR_RET_EXEC

RET instructions

executed.

This event counts the number of RET instructions that were

executed.

90H

00H

BR_RET_

MISSP_EXEC

Mispredicted RET

instructions executed.

This event counts the number of mispredicted RET

instructions that were executed.

91H

00H

BR_RET_BAC_

MISSP_EXEC

RET instructions

executed mispredicted

at decoding.

This event counts the number of RET instructions that were

executed and were mispredicted at decoding.

92H

00H

BR_CALL_EXEC

CALL instructions

executed.

This event counts the number of CALL instructions

executed.

93H

00H

BR_CALL_

MISSP_EXEC

Mispredicted CALL

instructions executed.

This event counts the number of mispredicted CALL

instructions that were executed.

94H

00H

BR_IND_CALL_

EXEC

Indirect CALL

instructions executed.

This event counts the number of indirect CALL instructions

that were executed.

97H

00H

BR_TKN_

BUBBLE_1

Branch predicted

taken with bubble 1.

The events BR_TKN_BUBBLE_1 and BR_TKN_BUBBLE_2

together count the number of times a taken branch

prediction incurred a one-cycle penalty. The penalty incurs

when:

ŌĆó Too many taken branches are placed together. To avoid

this, unroll loops and add a non-taken branch in the

middle of the taken sequence.

ŌĆó The branch target is unaligned. To avoid this, align the

branch target.

98H

00H

BR_TKN_

BUBBLE_2

Branch predicted

taken with bubble 2.

The events BR_TKN_BUBBLE_1 and BR_TKN_BUBBLE_2

together count the number of times a taken branch

prediction incurred a one-cycle penalty. The penalty incurs

when:

ŌĆó Too many taken branches are placed together. To avoid

this, unroll loops and add a non-taken branch in the

middle of the taken sequence.

ŌĆó The branch target is unaligned. To avoid this, align the

branch target.

A0H

00H

RS_UOPS_

DISPATCHED

Micro-ops dispatched

for execution.

This event counts the number of micro-ops dispatched for

execution. Up to six micro-ops can be dispatched in each

cycle.

A1H

01H

RS_UOPS_

DISPATCHED.PORT0

Cycles micro-ops

dispatched for

execution on port 0.

This event counts the number of cycles for which micro-ops

dispatched for execution. Each cycle, at most one micro-op

can be dispatched on the port. Issue Ports are described in

Intel® 64 and IA-32 Architectures Optimization Reference

Manual. Use IA32_PMC0 only.

A1H

02H

RS_UOPS_

DISPATCHED.PORT1

Cycles micro-ops

dispatched for

execution on port 1.

This event counts the number of cycles for which micro-ops

dispatched for execution. Each cycle, at most one micro-op

can be dispatched on the port. Use IA32_PMC0 only.

A1H

04H

RS_UOPS_

DISPATCHED.PORT2

Cycles micro-ops

dispatched for

execution on port 2.

This event counts the number of cycles for which micro-ops

dispatched for execution. Each cycle, at most one micro-op

can be dispatched on the port. Use IA32_PMC0 only.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel┬« CoreŌäó Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment